深入浅出理解UART协议

- 一、什么是UART?

- 二、UART的帧格式

- 2.1 为什么UART的传输需要起始位?

- 2.2 UART基本的数据形式

- 2.3 为什么UART的数据位可变?

- 三、UART的波特率

- 3.1 什么是波特率

- 3.2 如何换算波特率

- 3.3 波特率和采样频率是一样的吗?

- 四、UART协议中不同level工程师的不同考量

- 4.1 嵌入式开发人员

- 4.2 电路设计人员

- 4.3 IC设计人员

- 五、写在最后

- 六、其他数字IC基础协议解读

- 6.1 UART协议

- 6.2 SPI协议

- 6.3 I2C协议

- 6.4 AXI协议

一、什么是UART?

UART的全称是通用异步收发器(Universal Asynchronous Receiver/Transmitter)

Universal 通用性体现在UART使用范围广上,作为一个通用的接口协议,UART广泛的应用在各类MCU和SOC产品上。

Asynchronous 异步性体现在“不需要额外的时钟线进行数据的同步传输”即只要信号拉低,即可开始传送数据,而另一些通讯协议,需要引入时钟信号来进行操作,如AMBA,需要在时钟的上升沿发送数据

Receiver/Transmitter:收发器则更好理解,即一个数据的发送方和一个数据的接收方,也意味着在数字IC设计中需要分别设计Receiver和Transmitter

二、UART的帧格式

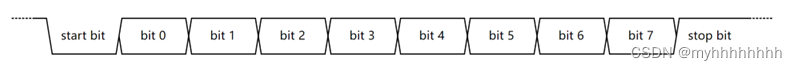

UART的一帧由起始位、数据位、校验位和停止位组成。数据逐位传输,如下图所示

2.1 为什么UART的传输需要起始位?

因为UART没有控制线,要让接收方知道什么时候开始接收数据,需要一些手段,UART数据的传输中,只有一根线,所以在发送数据之前,先发一位逻辑“0”作为数据发送的起始标志,接收方在空闲时,当检测到有一个低电平,则开始接逐位接收数据。

在具体设计UART的过程中,如何检测低电平,使用到了电平检测电路,可参考作者如下的文章

【数字IC手撕代码】Verilog边沿检测电路(上升沿,下降沿,双边沿)|题目|原理|设计|仿真

很显然这里使用的是下降沿检测电路

2.2 UART基本的数据形式

- 默认无传输数据时,为高电平

- 当信号拉低,传输线上的电平拉低,意味着开始进行数据传输

- 紧接着起始位的是数据位,它可以是5、6、7或8位。

- UART的“校验位”紧挨着“数据位”,采用奇偶校验方式,根据设置,校验位可以存在也可以不存在。

奇偶校验如何对应为Verilog设计案例同样可以参考作者之前的文章【数字IC手撕代码】Verilog奇偶校验|题目|原理|设计|仿真

- UART将停止位作为停止标志,是在数据位(没有校验位)和校验位(有校验位)之后发送1~2位的逻辑“1”高电平。当发送完停止位之后,UART总线进入空闲。

2.3 为什么UART的数据位可变?

因为UART是一种低速总线,每多发一位都占用不少的时间(由传输波特率决定),所以可以根据传输数据的特点,采用不同位宽以节约数据传输的时间。

三、UART的波特率

如果从更高的level审视UART传输协议,如嵌入式开发者的角度,我们会发现,在使用具体的UART协议前,我们需要对发送端和接收端进行波特率的同步,以此来确保发射端的数据可以在接收端得到正确的采集。常用的波特率可以是300,1200,2400,9600,19200,38400,115200,这些数意味着什么呢?别着急,我们接下来要讨论这个内容。

3.1 什么是波特率

波特率等于每秒钟传输的数据位数,假如我们的全局时钟频率为100MHz,波特率设置为9600,那么意味着每秒该UART传输协议可以传输9600bits的数据,换句话说传输1比特需时间约为:10^9(ns)/9600=104166(ns)。

3.2 如何换算波特率

书接上文,时钟频率假如为100MHz,这意味着我们的时钟周期为10ns,因此10416个时钟周期我们就可以传输1bit数据,换言之我们需要一个大小为10416的分频电路来对100MHz时钟进行处理,因此在设计UART的过程中,我们需要使用分频电路依据波特率处理全局时钟,依据分频后的时钟节奏来发送数据和接收数据。

同样的,参考作者之前的文章,我们可以获知分频电路的设计方法

【数字IC手撕代码】Verilog奇数分频|题目|原理|设计|仿真

【数字IC手撕代码】Verilog偶数分频|题目|原理|设计|仿真

【数字IC手撕代码】Verilog半整数分频|题目|原理|设计|仿真

【数字IC手撕代码】Verilog小数分频|题目|原理|设计|仿真

3.3 波特率和采样频率是一样的吗?

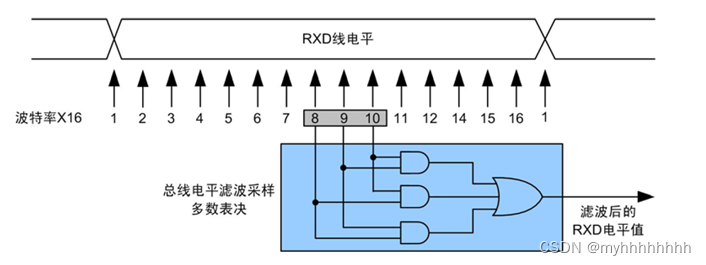

按照前文所说,好像波特率和采样频率是一个意思,即9600波特率对应接收端1s进行9600次采样,也对应发射端1s进行9600bit的发射,那么请读者思考,真的是这样吗?

答案其实是否定的

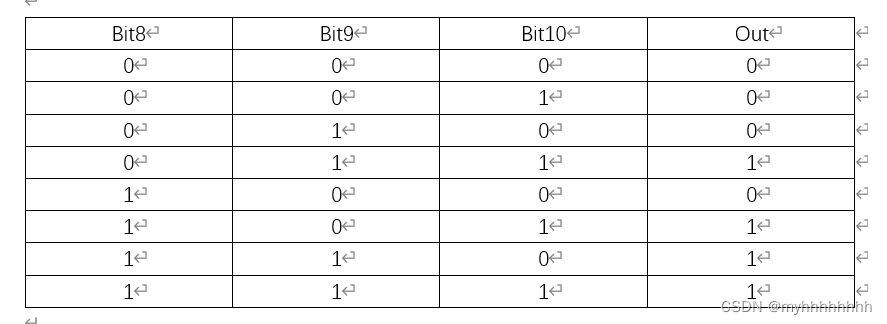

这是因为:在数据的传输中,信号可能受到一些干扰而产生一些抖动(比如说电磁兼容性设计中的近端串扰),如果接收端只对这些信号进行一次采样,那么它有可能采样到的是不准确的数据,所以接收端在采样时,通常都要采样多次,然后通过处理获得准确的数据,比如说,我们可以用多数表决的方法来在接收端进行多次采样,得到准确值,下图展现了16倍频采样的多数表决电路结构和它的真值表。

通过对真值表的观察,我们可以发现,使用三个与门与一个异或门,我们实现了多数表决的功能,(即有两bit为1即输出为1,两bit为0则输出为0)

四、UART协议中不同level工程师的不同考量

4.1 嵌入式开发人员

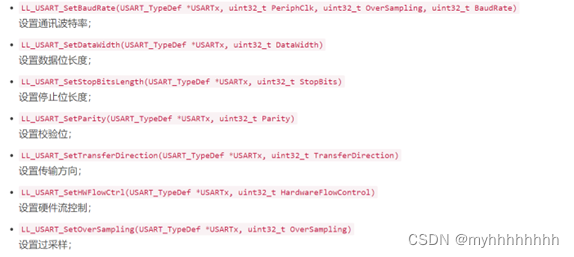

对于嵌入式开发人员来说,在库函数包装到位的情况下在使用UART的过程中需要进行如下的设置,通过编程语言设置它的波特率,长度,校验位等特性。

4.2 电路设计人员

对于电路设计工程师而言,需要考虑UART的电气特性,比如RS232形式的UART协议中**“逻辑“1”为-3V~-15V”,逻辑“0”为+3~+15V**。首先-15V到15V的电压范围肯定与MCU输出的电压不同,其次RS-232形式的UART与RS-485形式的UART在具体的特性上也存在诸多不同,这里就需要电路层面上的“RS-232电平转换电路”等结构的帮助。

4.3 IC设计人员

而对于IC设计工程师来说,则需要考虑使用硬件描述语言将嵌入式开发中所需要使用到的如波特率,数据位数,奇偶校验,采样频率,等一一使用Verilog语言进行翻译,并留出可配置的寄存器,来打通软硬件之间的界限,因为作者对于IC设计更为了解,所以本文的更多的从IC设计的角度来进行思考

五、写在最后

接下来的文章,我们将从零开始使用Verilog设计一个UART出来,并进行不那么充分的验证工作,其中UART具体满足的参数如下

- 单工UART,收/发器固定;

- 支持5-8位数据位、1/2位停止位、可选1位奇偶校验位;

- 奇偶校验结果错误的检测能力;

- 波特率可调;

详情可参见- 【数字IC】从零开始的Verilog UART设计

六、其他数字IC基础协议解读

6.1 UART协议

- 【数字IC】深入浅出理解UART

- 【数字IC】从零开始的Verilog UART设计

6.2 SPI协议

- 【数字IC】深入浅出理解SPI协议

- 【数字IC】从零开始的Verilog SPI设计

6.3 I2C协议

- 【数字IC】深入浅出理解I2C协议

6.4 AXI协议

- 【AXI】解读AXI协议双向握手机制的原理

- 【AXI】解读AXI协议中的burst突发传输机制

- 【AXI】解读AXI协议事务属性(Transaction Attributes)

- 【AXI】解读AXI协议乱序机制

- 【AXI】解读AXI协议原子化访问