亲爱的大疆你考的这都是啥

单选题(共11道题)

1.【单选题】下列关于stuck-at故障模型描述错误的一个是:

A.组合逻辑上的Fault点可以做故障合并

B.用于覆盖内部得时序故障

C.正常Capture阶段只有1个Pulse

D.对于Full-scan设计可以达成很高得故障覆盖率

解:不懂这个瞎选的

C

故障模型和故障建模 - HarryPotterIsDead! - 博客园

2.[单选题]下列关于芯片中电迁移的描述错误的一个是:

A.用电迁移会降低芯片寿命

B.电迁移会使芯片性能退化

C.增加导线宽度可以修复电迁移违例

B.增加导线间距可以修复电迁移违例

解:C

B

电迁移(EM)是一种分子位移,是由于导电电子和离子在一段时间内的动量转移而引起的。当电流密度较高时会发生这种现象,这会导致金属离子向电子流方向漂移。EM通常发生在现场设备部署多年之后。

导线的电迁移可靠性:

A =横截面积依赖常数

Jn =电流密度

E a =活化能(Activation energy )

k =玻尔兹曼常数

T =开尔文温度

N =比例因子(通常根据黑色设置为2)

电迁移缓解

1. 对EM违规网络应用NDR(非默认规则)

获得EM结果后,您可以获取净形状并使用NDR重新路由这些网络。应用NDR涉及使用具有更大间距的双宽或三宽金属来布线时钟网络。这将快速消除大多数EM违规行为,甚至可以预测网络,这些网络更可能基于两个参数进行EM违规:

1)驱动强度

2)负载。

可以过滤掉更多负载和高驱动的网络,并将它们移动到NDR。可以根据项目统计数据决定不同驱动强度的阈值负载。

示例:我们看到其中一个单元出现了惊人的改进

Command: create_routing_rule em_ndr -widths“M2 0.064 M3 0.064 M4 0.064”-cuts {{VIA1 {Vrh 1} {Vrv

1}} {VIA2 {Vrh 1} {Vrv 1}} {VIA3 {Vrh 1} {Vrv 1}} {VIA4 {Vr 1}}}

foreach net [gon [get_nets $ nets]] {set_routing_rule $ net -rule em_ndr}

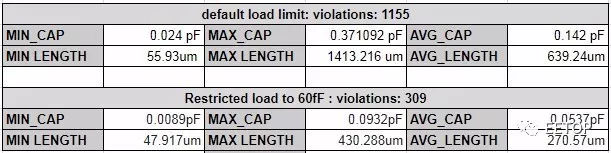

这些设置之前,有309次违规,在应用NDR后减少为1次。

2. 限制网络的负载目标

限制或减少负载也可有助于防止电迁移的发生。在上面的例子中,我们看到142fF是设计中的平均电容。根据一些实验的统计数据,我们限制所有网络的最大负载为60fF。结果,我们看到信号EM和平均净长度都有很好的改善。

Command:set_max_capacitance 0.06 [current_design] #setting max_cap_value用于设计

缓解 IR 压降

1. Padding clock cells

当涉及到IR时钟问题时,由于高时钟切换,时钟结构是芯片功耗的主要原因。然而,利用 Padding clock cells 技术,时钟缓冲器/反相器和时钟门单元被赋予额外的区域作为禁止布线区,以避免标准单元的放置和它们周围任何过量的单元密度。这有助于防止动态IR压降。

Command: create_keepout_margin -outer {3.6 0.576 3.6 0.576} $clock_type_keepout IMAGE: A cell with cell padding

2. Cell Padding/Decap insertion around cells within a dynamic IR hotspot region

一些驱动强度高的单元会产生动态IR压降问题。可以为这些单元提供单元衬垫,或者在其周围或IR压降区域插入decap单元格,以防止IR 压降问题。

3.[单选题]下列会直接影响到芯片工作频率的一个违例是:

A.建立时间违例

B.保持间距违例

C.最大转换时间违例

D.最大扇出违例

解:A

4.[单选题]从奈奎斯特采样定理得出,要使实信号采样后能够不失真还原,采样频率f与信号最高频率fs的关系时( )

A.f大于等于2fs

B.f小于等于2fs

C.f大于等于fs

D.f小于等于fs

解:A

5.[单选题]以下是对Cache-主存-辅存三级存储系统中各级存储器的作用,速度,容量的描述,其中完全正确的是

A.主存用于存放CPU正在执行的程序,速度慢,容量较大

B.Cache于存放CPU当前访问频繁的程序和数据、速度快、容量小

C.辅存用于存放需要联机保存但暂不执行的程序和数据,速度快,容量极大

D.加大Cache的容量可以使主存能够存放更多的程序和数据

解:B 计算机组成原理

C 太慢了,巨慢

CPU速度 > 内存速度 > 硬盘速度

计算机的主存是指下边两个:

1.RAM:random access memory ,随机存取存储器,即我们电脑的内存条;

2.ROM:read only memory ,只读存储器,这种存储器用途比较少,一般就是电脑中存放boot的地方,我们启动电脑的时候,电脑先读ROM中的内容,比如我们的BIOS系统,先检测我们电脑的硬件是否正常,这个ROM在电脑主板第一次生产的时候就写进入了,只能往外读了,不能再写了

计算机的辅存是指:

就是一些外部存储器,比如硬盘、光盘、U盘等

6.[单选题]关于linux命令,下面说法错误的是:

A.find.-name,“*.txt”命令会列出当前目录及子目录下所有以txt结尾的文件

B.mv master.map master1.map命今的作用是把master.map文件复制成master1.map

C.要解压缩一个名字为test.tar.gz的文件可以使用命令tar-xzvf test.tar.gz

D.linux令行中输入cmd1&&cmd2(其中cmd1及cmd2是两个命令),如果cmd1执行失败了,cmd2就不会执行

解:B 重命名

7.[单选题]关于综合工具,以下说法正确的是:

A.一般为了综合效率,综合工具使用越新越好

B.综合工具越来越强大,所以对于一些不可综合的逻辑也没有问题

C.综合工具一般需要和Formal工具配套使用

D.综合工具使用一个固定版本效果最好

8.[单选题]运行以下程序输出的值是

int addr = 32'ha; //'b1010

bit is_legal = 1;

bit[33.0]info0;

initial begin

if(addr[0])

is_legal = 0;

else

Is_legal = 1; //is_legal = 0

info0 = ~is_legal;//info0=1

info0 =(info0,addr);//1的地址是a

info0 =(info0,0);//1的地址是0

$display(“0x%0h”.info0);//因为addr是32bit 所以就是1_0000_0000

endA.0x1_0000_0000

B.0x2_0000_0000

C.0x14

解:

我感觉选A

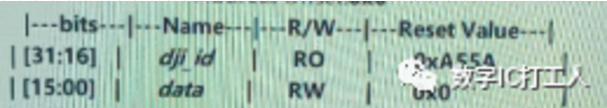

9.[单选题]DUT中有一个寄存器"DJI_ID_HEAD",该DUT通过APB总线端口与SoC互联,

"DJI_ID_HEAD"寄存器的描述如下:

Name:DJI_ID_HEAD

Address Offset:0x0

通过寄存器模型对"DJI_ID_HEAD"寄存器进行如下程序所示的读写访问,

uvm_status_e status;

uvm_reg_data_t rvalue ,

RGM.DJI_ID_HEAD.read(status,rvalue,UVM_FRONTDOOR);

RGM.DJI_ID_HEAD.write(status,16'hFFAA,UVM_FRONTDOOR);

RGM.DJI_ID_HEAD.data.get0;

RGM.DJI_ID_HEAD.data.set(16'hFFAA);

RGM.DM ID HEAD.update(status)

RGM.DJI_ID_HEAD.data.set(16'hAAFF);

RGM.DJI_ID_HEAD.update(status);

RGM.DJI_ID_HEAD.reset();

RGM.DJI_ID_HEAD.data.set(16'hAAFF);

RGM.DJI_ID_HEAD.update(status);

RGM.DJI_ID_HEAD.read(status,rvalue,UVM_FRONTDOOR);

RGM.DJI_ID_HEAD.mirror(status);

请问在DUT的APB总线端口上能看到多少笔有效的数据传输?

(选项忘拍了,当简答作吧)

这啥啊都。。。

10.[单选题]假设:class trans_ext extends trans_base;

int a = 0;

endclass,

以下代码可以正确打印出a伯的选项是:

A.trans_ext tr_el;

trans_ext tr_e2;

trans_base tr_b;

tr_el = new();

tr_b = tr_el;

$cast(tr_e2,tr_b);

$display(''a is %0d'',tr_e2.a);

B.trans_ext tr_el;

trans_ext tr_e2;

trans_base tr_b;

tr_el = new();

tr_b = tr_el;

$cast(tr_b,tr_e2);

$display(''a is %0d'',tr_e2.a);

C.trans_ext tr_el;

trans_ext tr_e2;

trans_base tr_b;

tr_el = new();

tr_b = tr_el;

$cast(tr_e2,tr_e1);

$display(''a is% 0d'',tr_e2.a);

D.trans_ext tr_el;

trans_ext tr_e2;

trans_base tr_b;

tr_el = new();

tr_b = tr_el;

$cast(tr_e1,tr_e2);

$display(''a is%60d'',tr_e2.a);

解:不懂验证。。

11.[单选题]systemverilog语句,已知:

int arr[2][ ][ ];

arr[0]=new[4];

以下哪个操作是合法的:

A.arr[0][0]=new[2];

B.arr[1][0]=new[2];

C.arr[0][ ]=new[2];

D.arr[0][1][1]=new[2];

解:

多选题(共5道,每道5分,共25分)

1.[多选题]下列属于DFT故障模型的是:

A.stuck-at

B.transition-delay

C.brige

D.IDDQ

解:ACB 看第一个题的连接

2.[多选题]下列属于芯片中时钟树综合质量评价指标的有:

A.时钟网络延时

B.时钟信息偏差

C.时钟周期

D.时钟树功耗

解:ABCD abd

3.[多选题]下列属于降低芯片静态压降的方法有:

A.增大电源网络密度

B.减小封装电感

C.增加芯片内电容

D.降低工作效率

解:BD 不懂

4.[多选题]关于异步处理,以下说法正确的是

A.静志配置信号可以不做异外理

B.异步处理需要考虑发送和接收时钟之间的频率关系

C.异步FIFO采用格雷码的原因是为了提高电路速度

D.单比特信号打两拍后可以避免亚稳态的发生

解:AB 因为bc错所以ab对

5.[多选题]以下哪一种门电路属于通用逻辑门(可以组合搭建出任何逻辑电路)

A.AND

B.NAND

C.OR

D.NoR

E.XOR

解:BD 还有个反相器not