如果很多操作步骤忘记可以参考链接: Quartus II实验一 运算部件实验:加法器![]() https://blog.csdn.net/qq_45037155/article/details/124202068

https://blog.csdn.net/qq_45037155/article/details/124202068

本实验需要建立三个工程文件

1. 设计一个4位求补器

2. 设计一个4·4的不带符号的阵列乘法器

3. 设计一个5·5的带符号的阵列乘法器

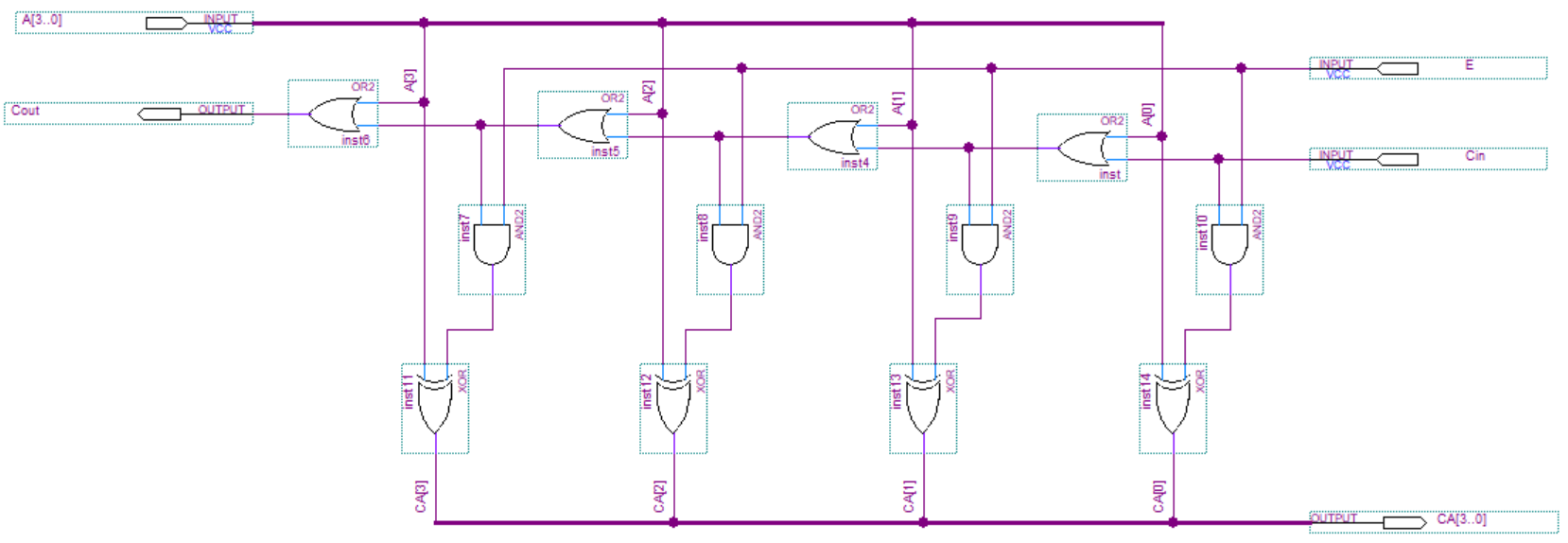

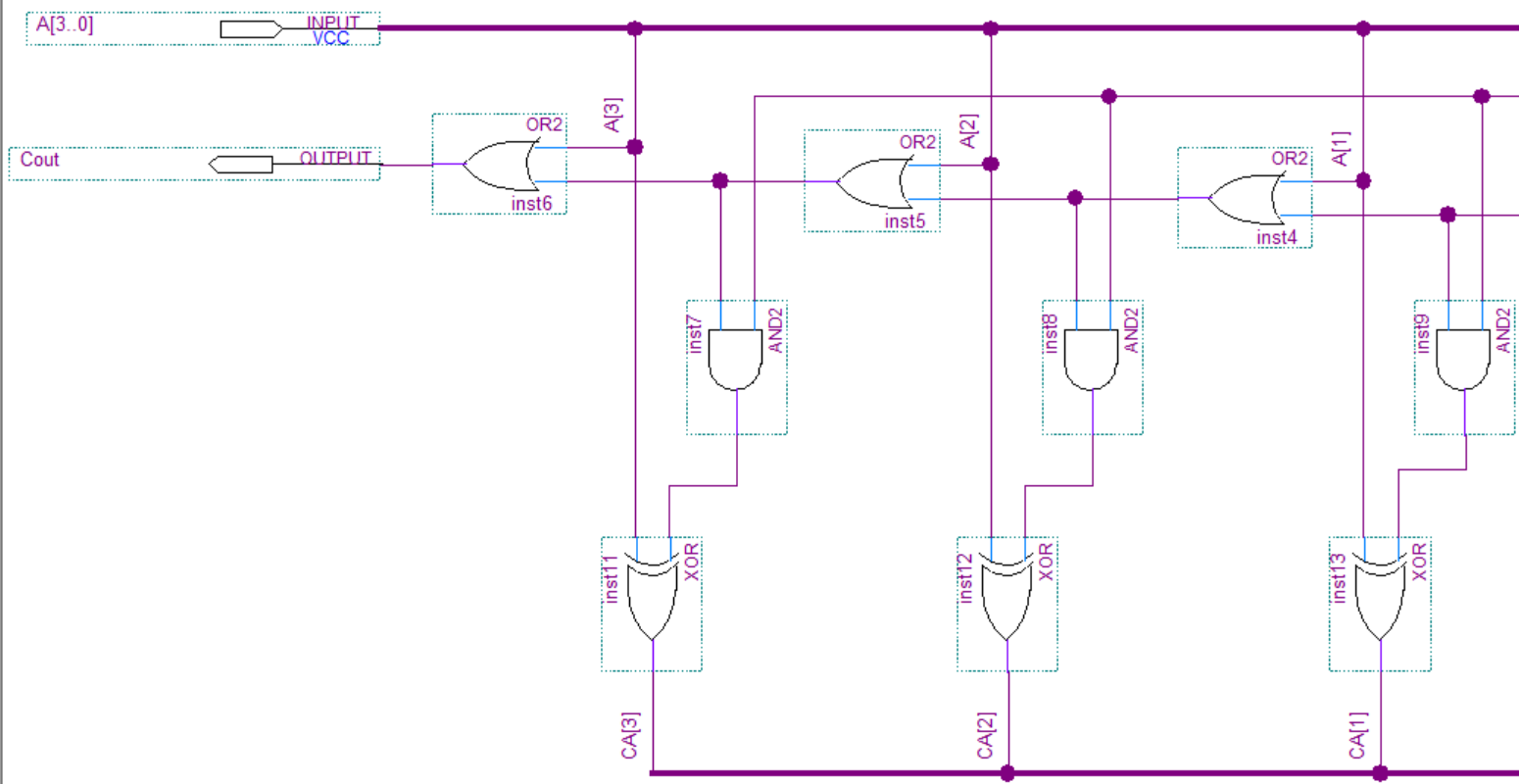

一、 建立一个工程,设计4位求补器,并加以仿真

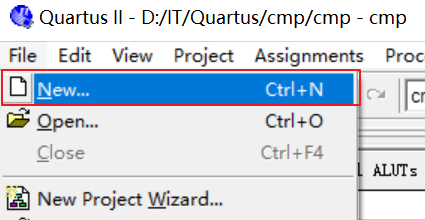

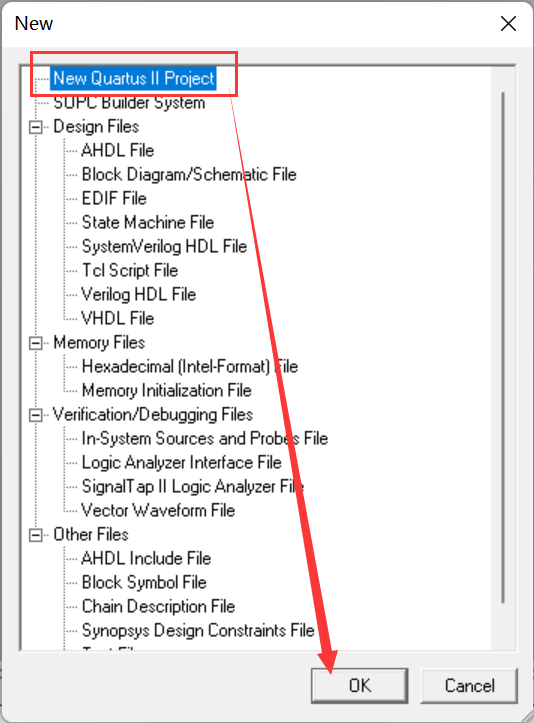

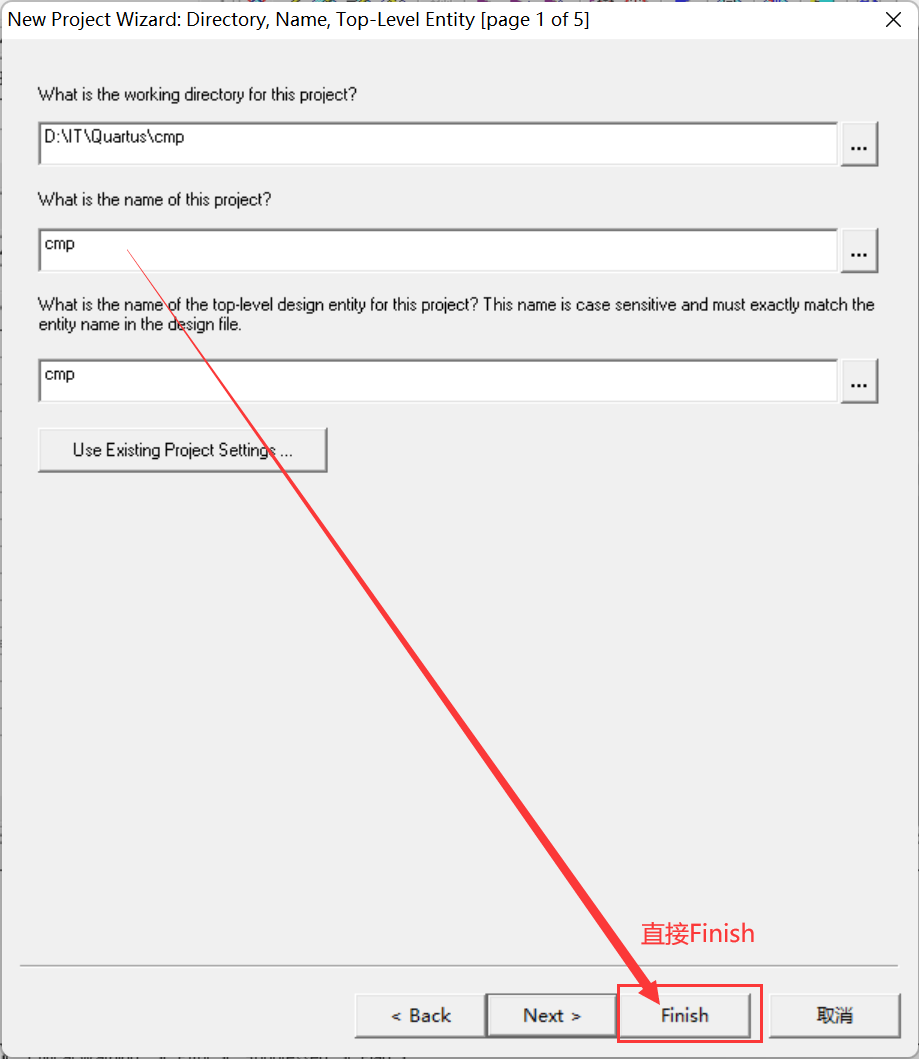

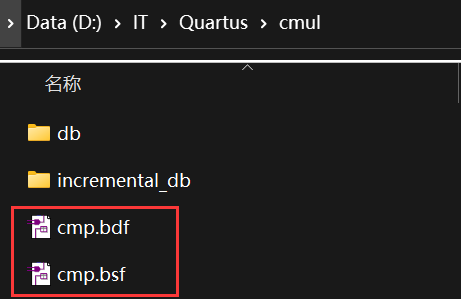

1. 新建工程 cmp

(1)保存位置 D:ITQuartuscmp

工程名称 cmp

主文件(top-level design entity)cmp

2. 设计原理图文件保存为cmp.dbf

(1)新建——Block Diagram,保存为cmp

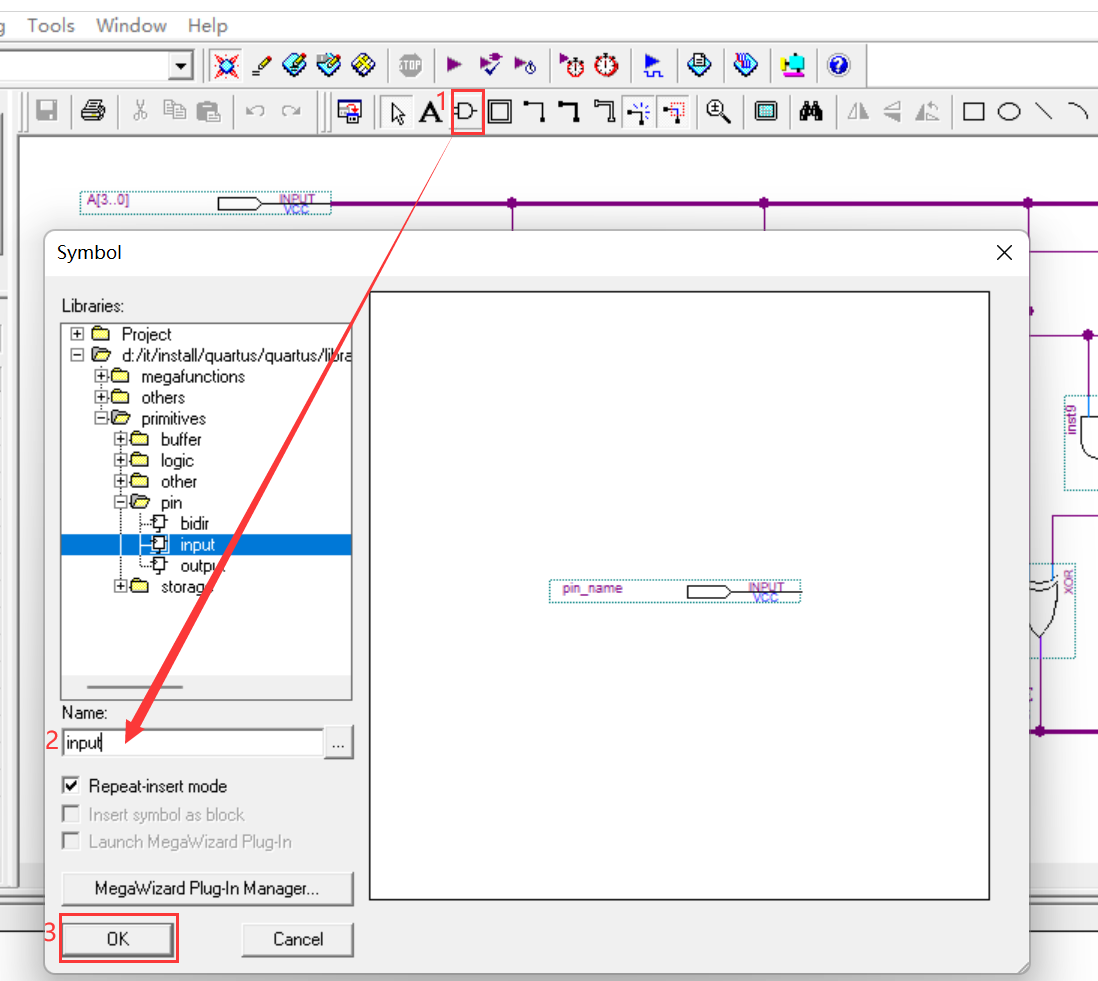

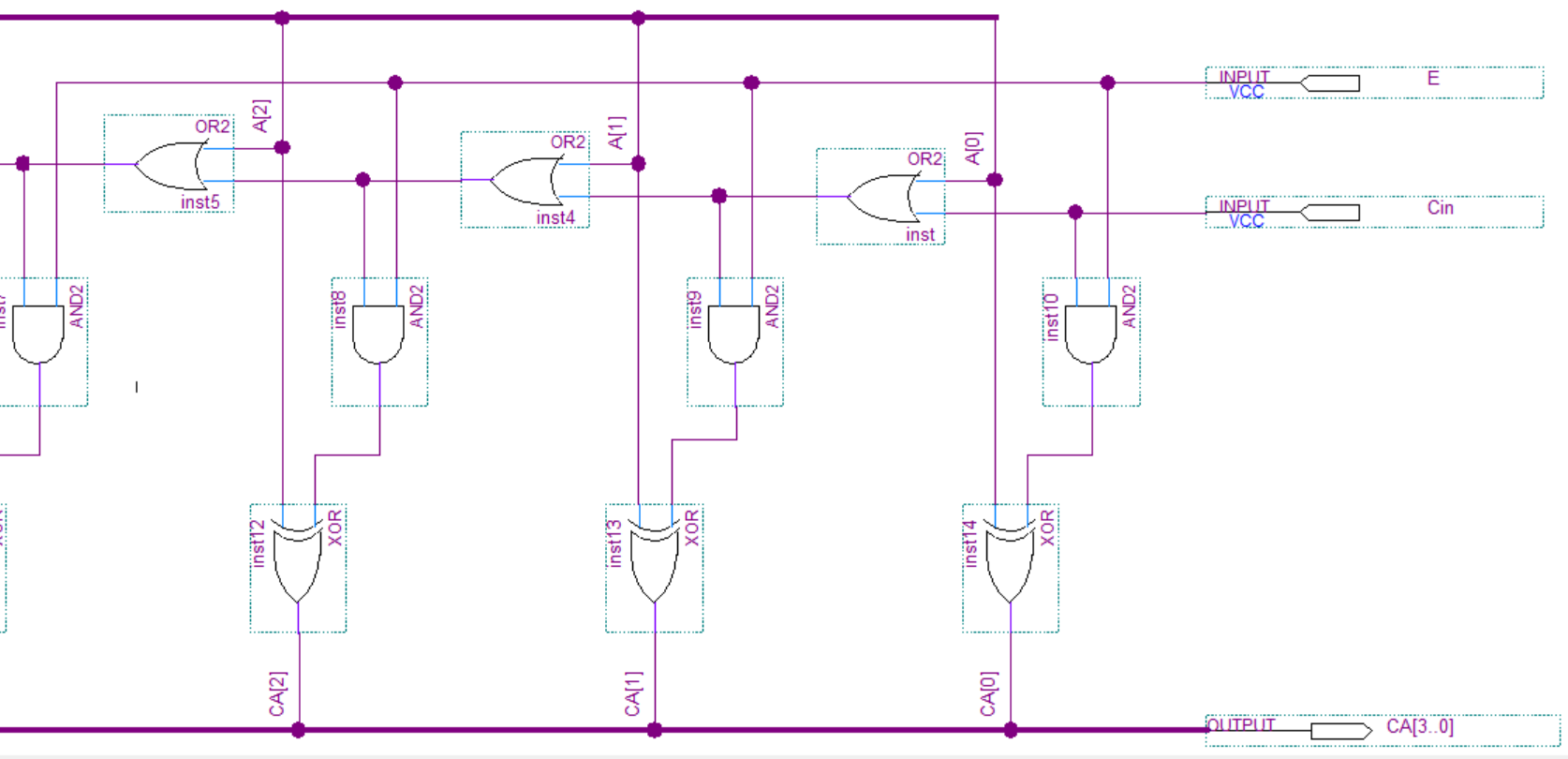

(2)添加元件:

输入信号、输出信号、2与门、2或门、异或门

Input output and2 or2 xor

修改输入信号依次位A[3..0]、Cin、E

输出信号依次为 CA[3..0]、Cout

(3)设置Cin和Cout的目的

a. 扩展4位求补器,构成4*n位的求补器

b. 低位求补器的Cout传递低位求补器是否有1的信息,

c. 高位求补器的Cin用于接收低位Cout的信息。

(4)连接元件

这里强调注意点:

a. OK选中后在图上单击即可显示,按键Esc退出使用,Delete删除

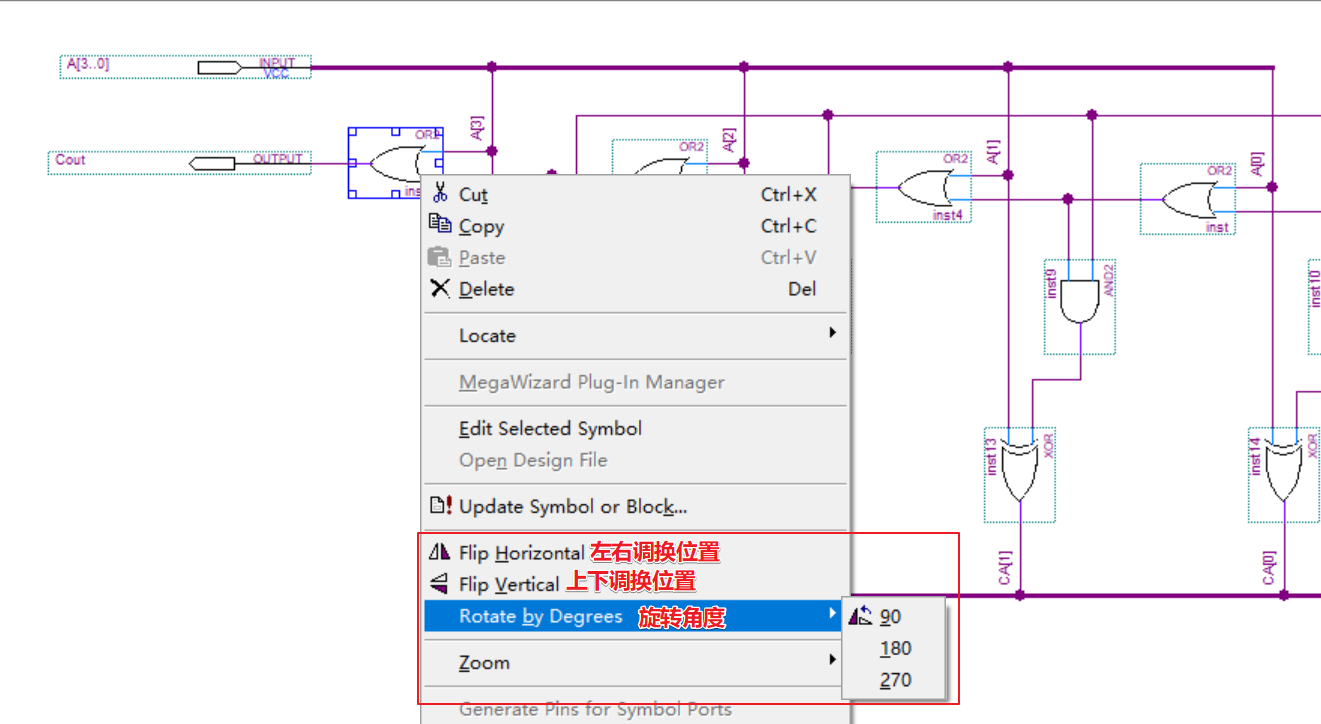

b. 对于图的形态变化如图操作

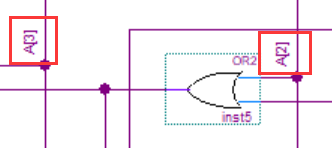

c. 数据源一定不能忘记添加【它的方向与线横竖一致】

(5)效果显示

a. 全局显示

b. 左局部显示

c. 右局部显示

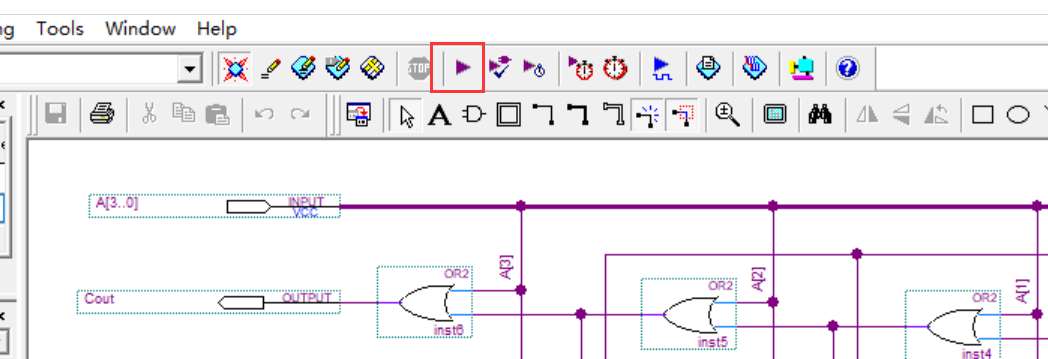

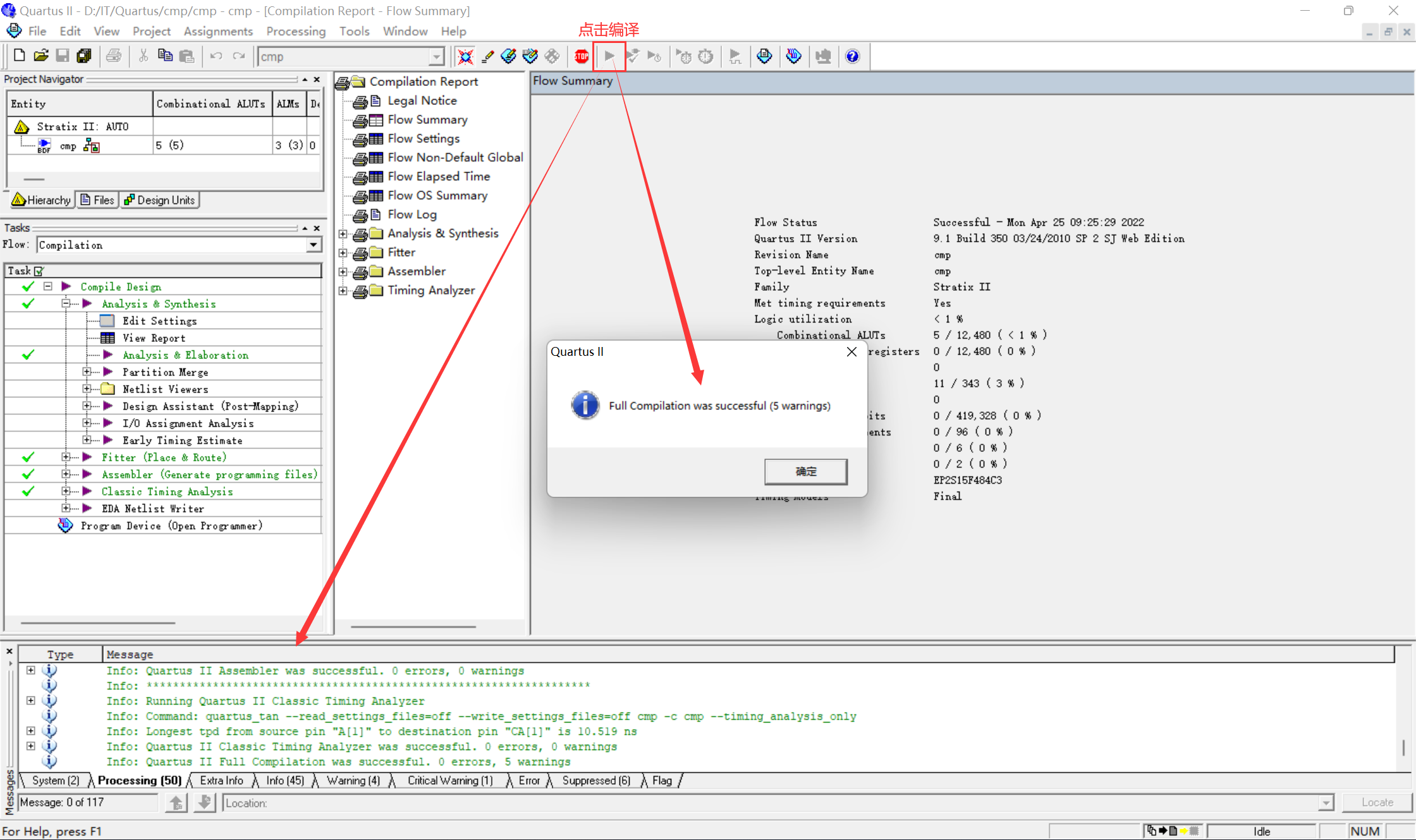

(6)编译

3. 设计仿真波形文件保存为cmp.vwf

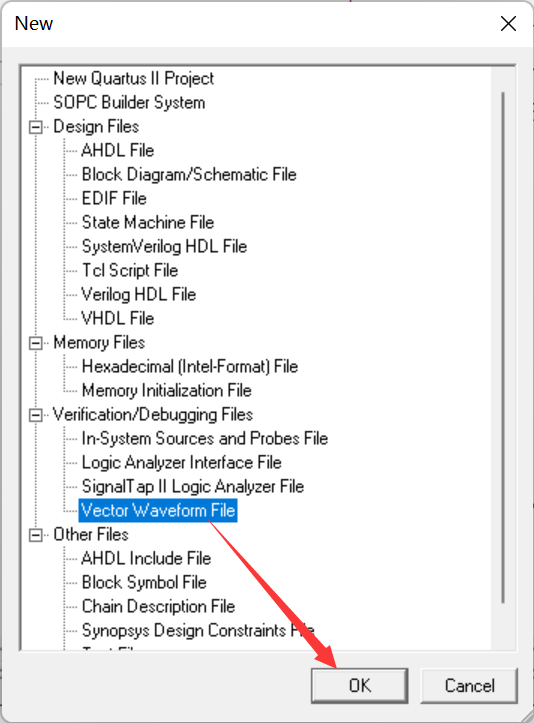

(1)新建——Vector Waveform File

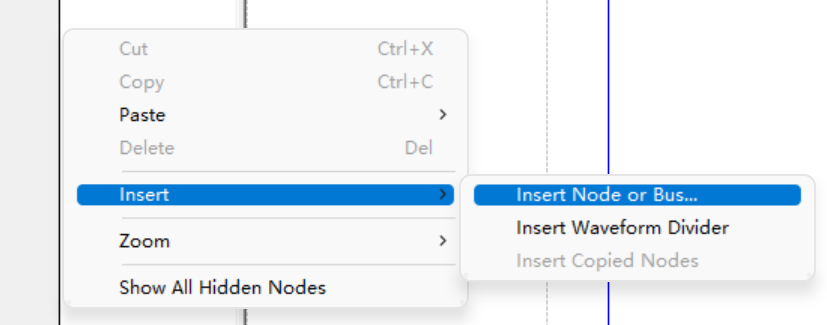

(2)插入仿真的信号(快捷菜单——inert node or bus——node finder)

参考实验一链接操作吧

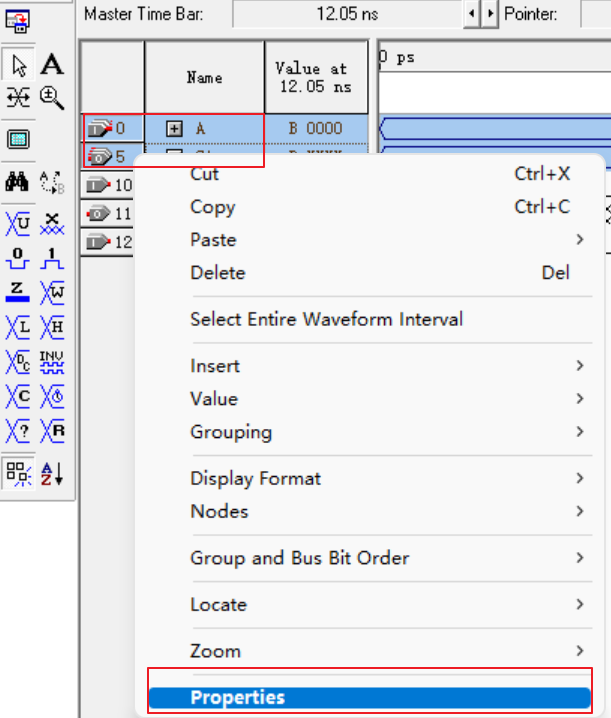

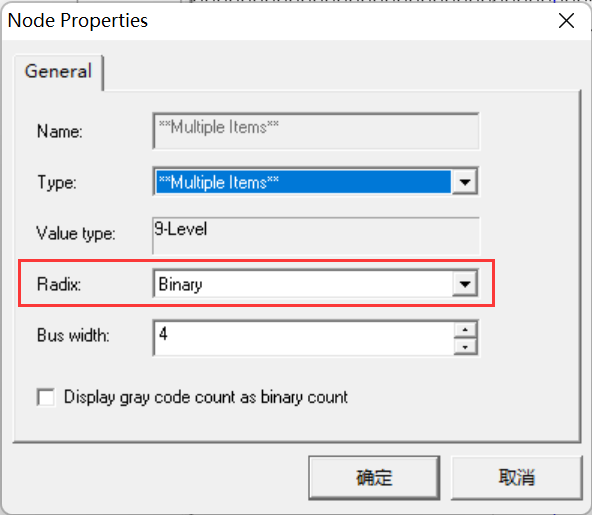

设置A 、CA的显示格式为binary

设置仿真信号,要求

Cin、E有00、01、10、11四种情况

A为多个随机二进制数

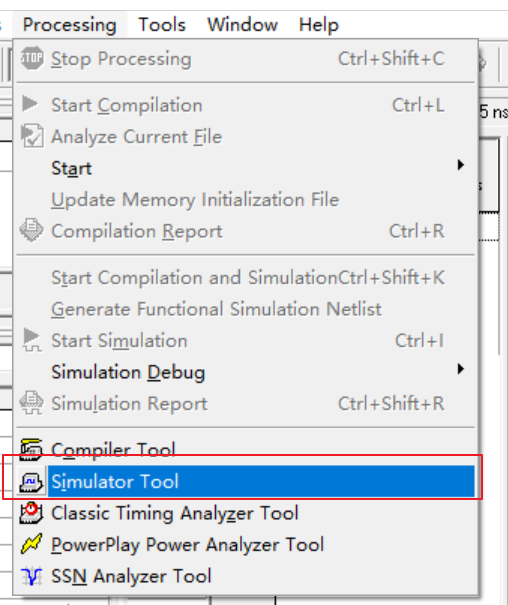

(3)Processing ——simulation tools 仿真

选择——functional 进行功能仿真(生成功能仿真的网表文件)

Start——开始仿真

Report——查看仿真结果

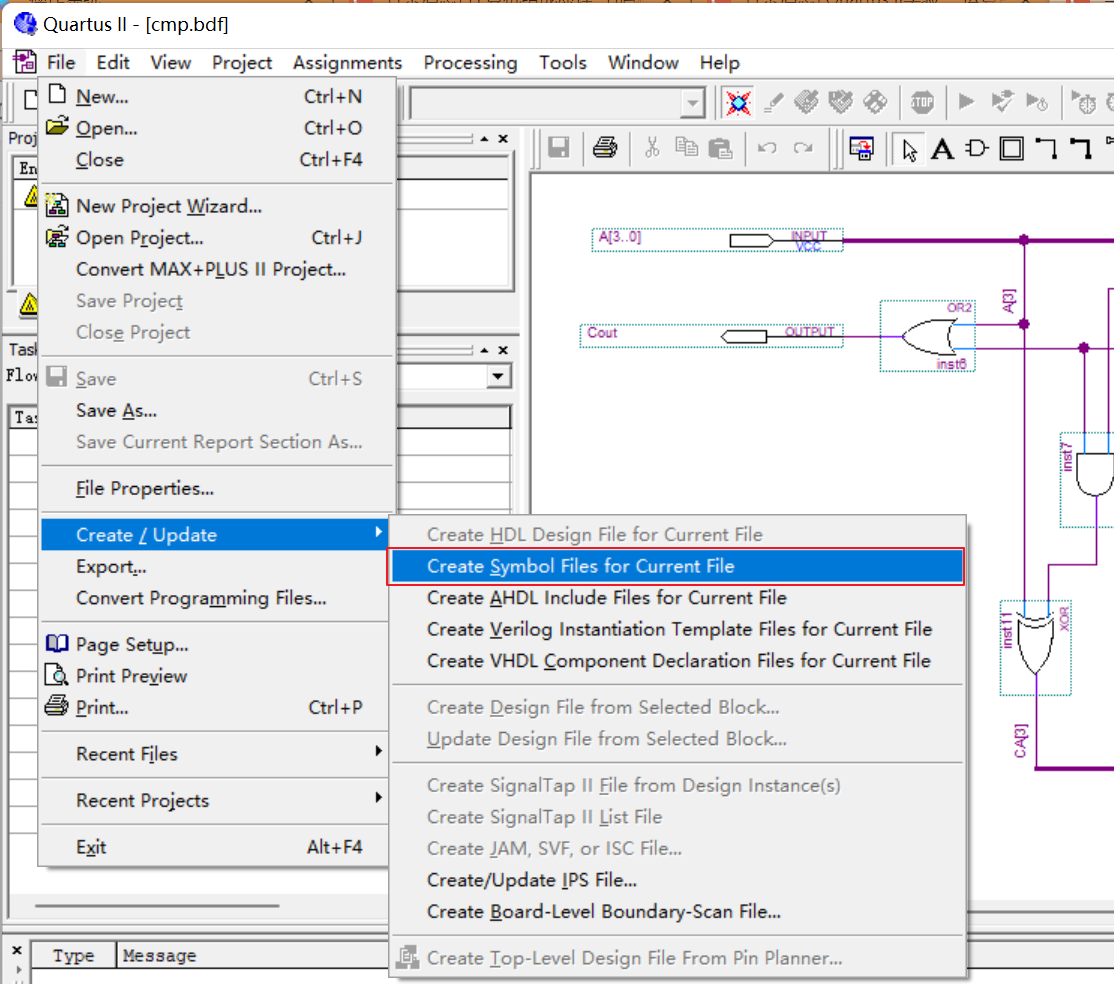

4. 用原理图文件cmp.bdf,创建symbol文件cmp.bsf

(1)文件——Create/Update——Create Symbol File for Current File

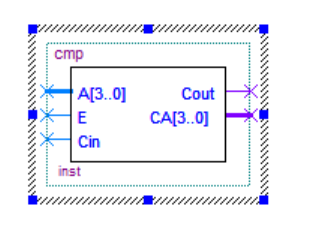

cmp.bsf 显示如下

注意:下面俩个工程和第一个工程操作步骤一致,不做详细图解说明了

二、 建立一个工程,设计4×4不带符号的阵列乘法器,并加以仿真

1. 新建工程mul

(1)保存位置 D:ITQuartusmul

工程名称 mul

主文件(top-level design entity)mul

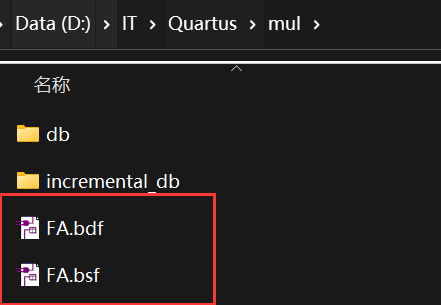

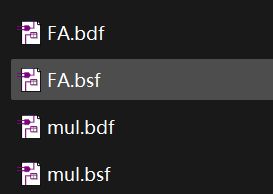

(2)拷贝 FA.bdf 和 FA.bsf 到 D:ITQuartusmul

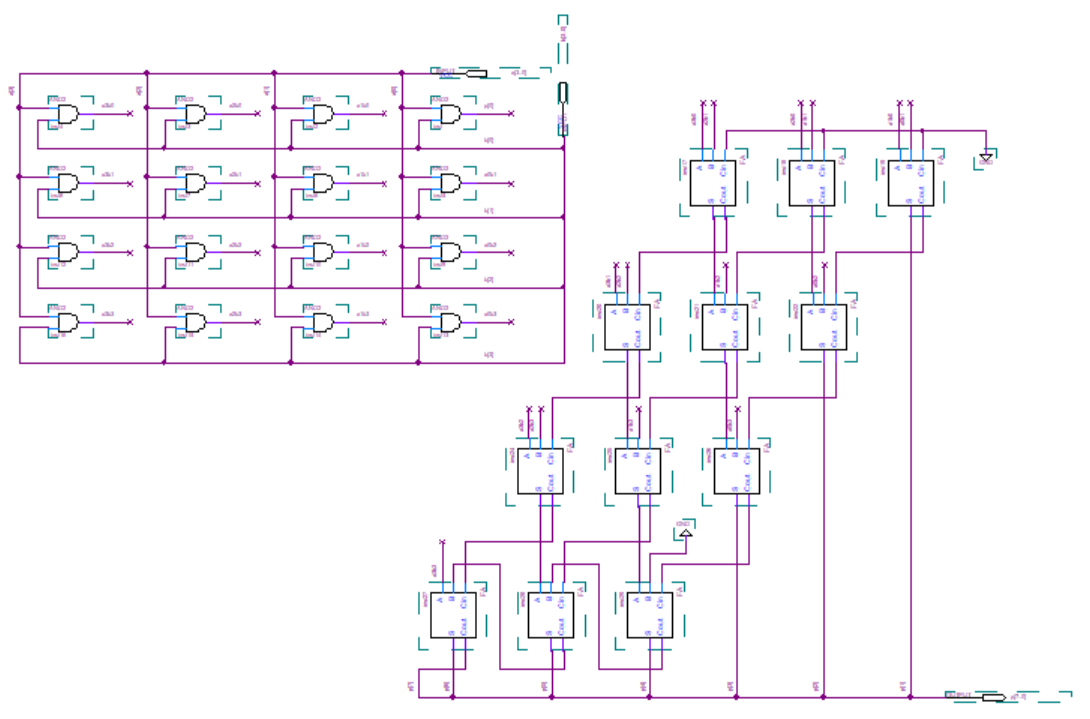

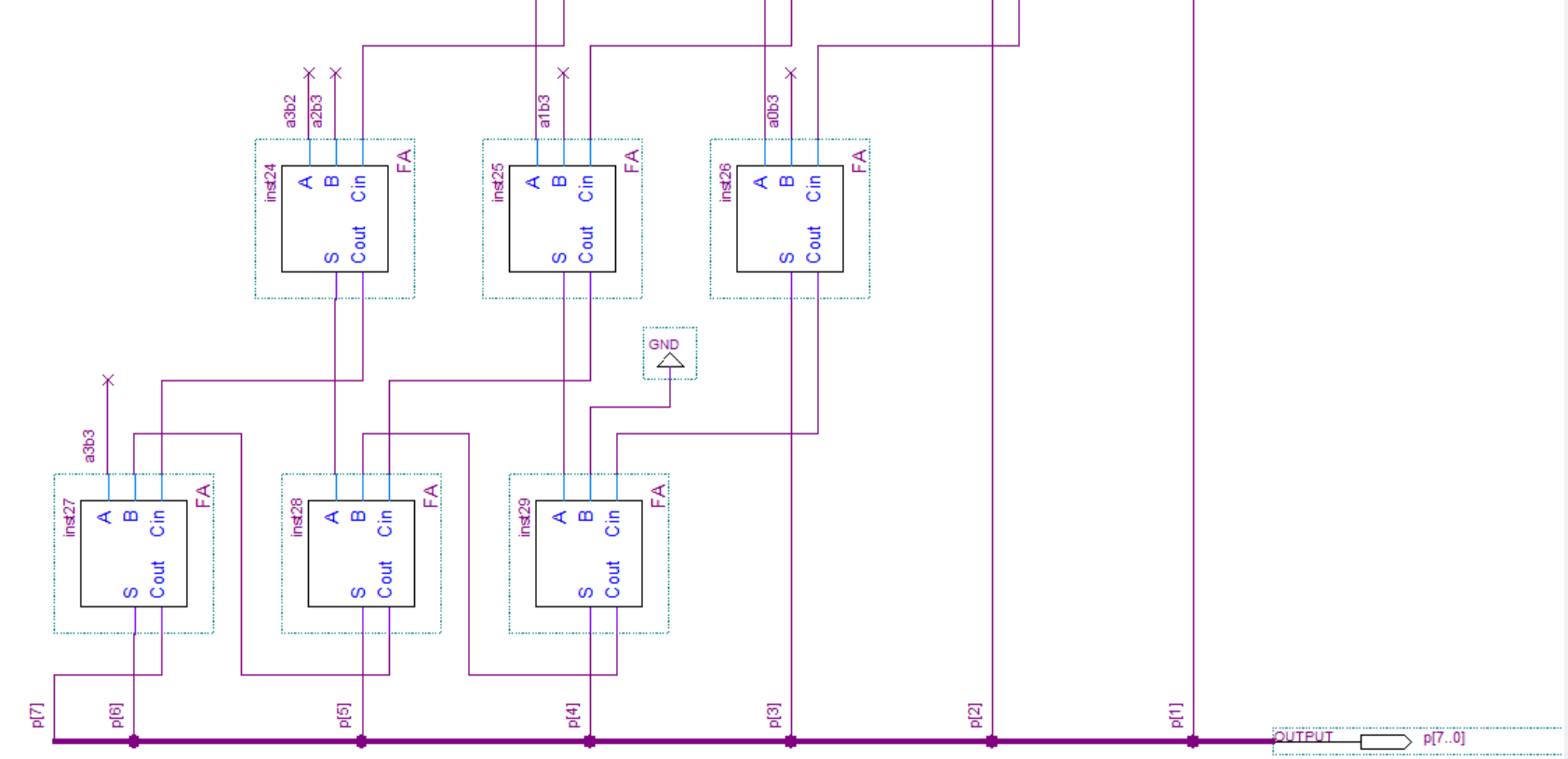

2. 设计原理图文件保存为mul.bdf

(1)新建——Block Diagram,保存为mul

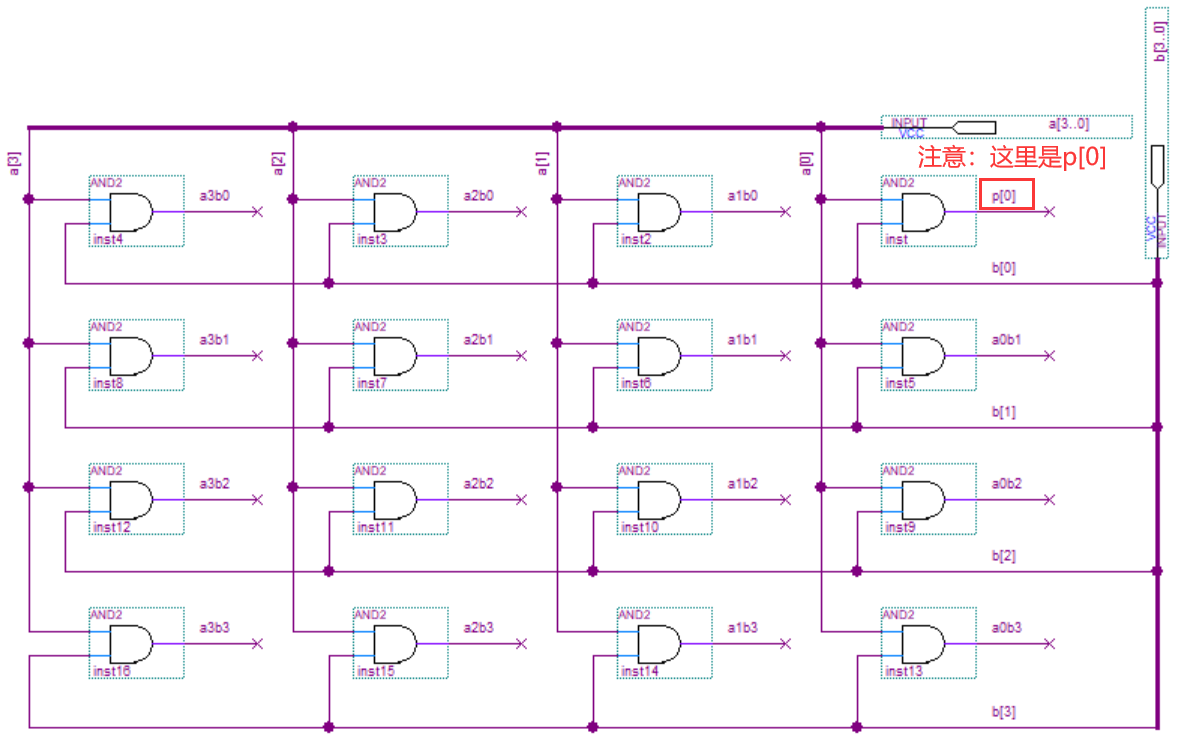

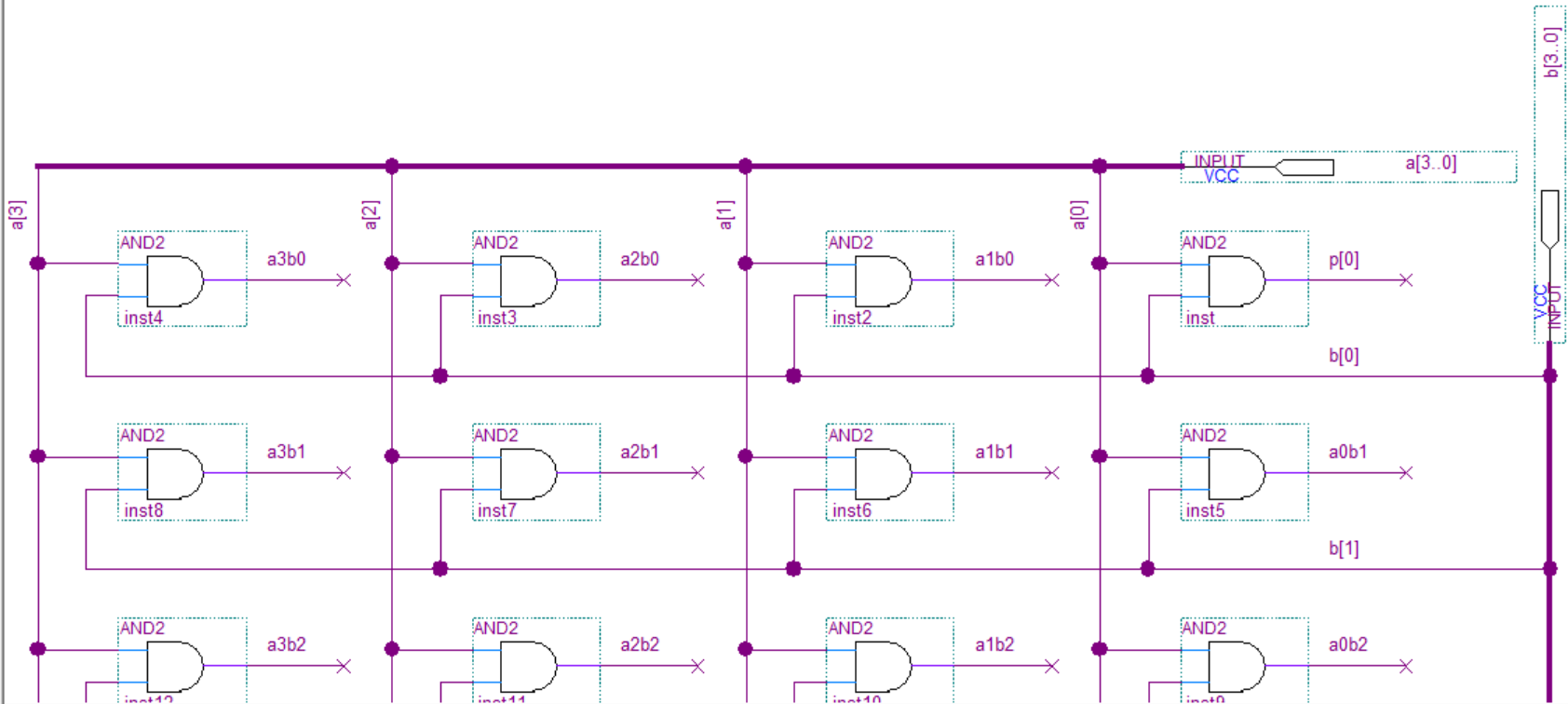

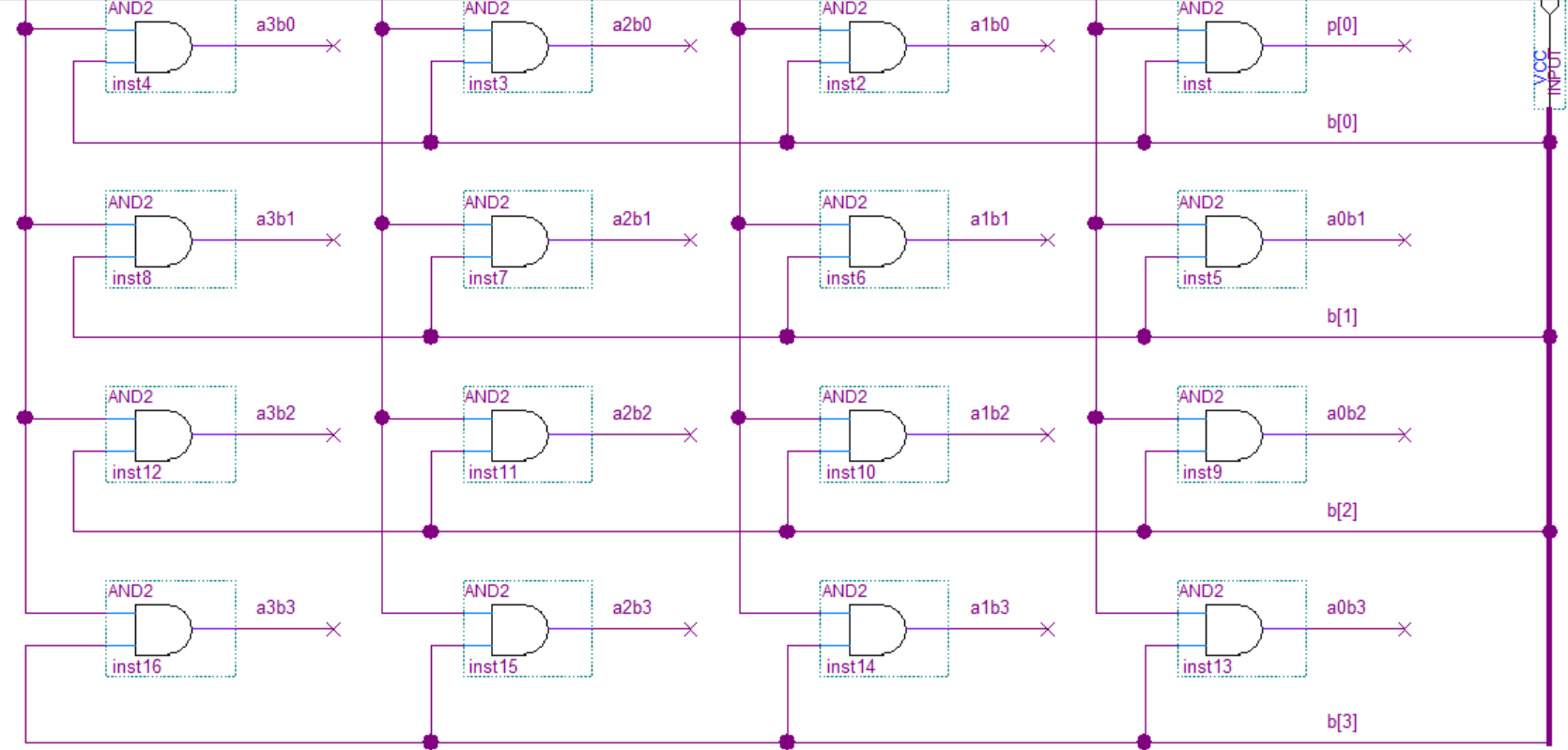

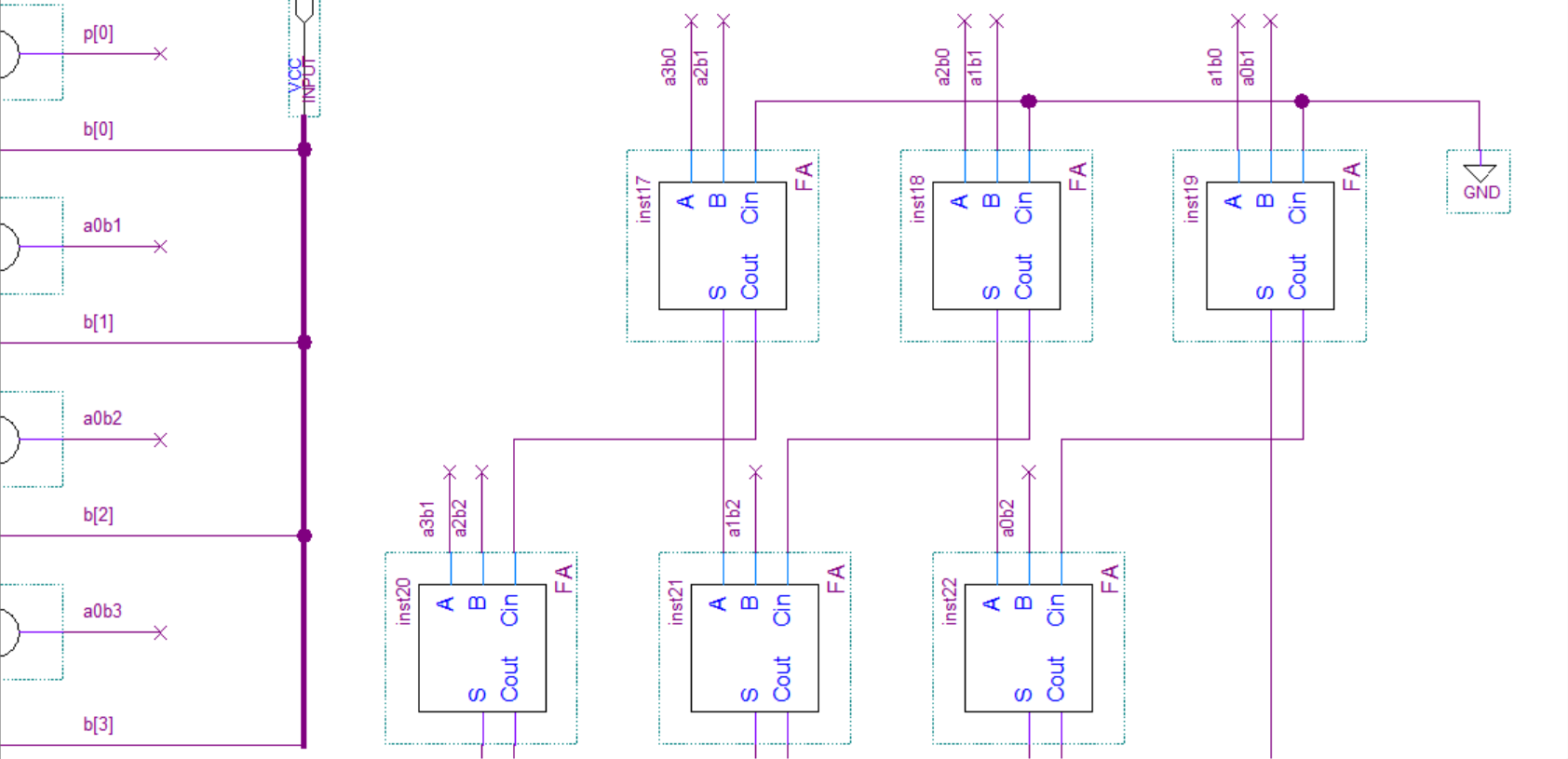

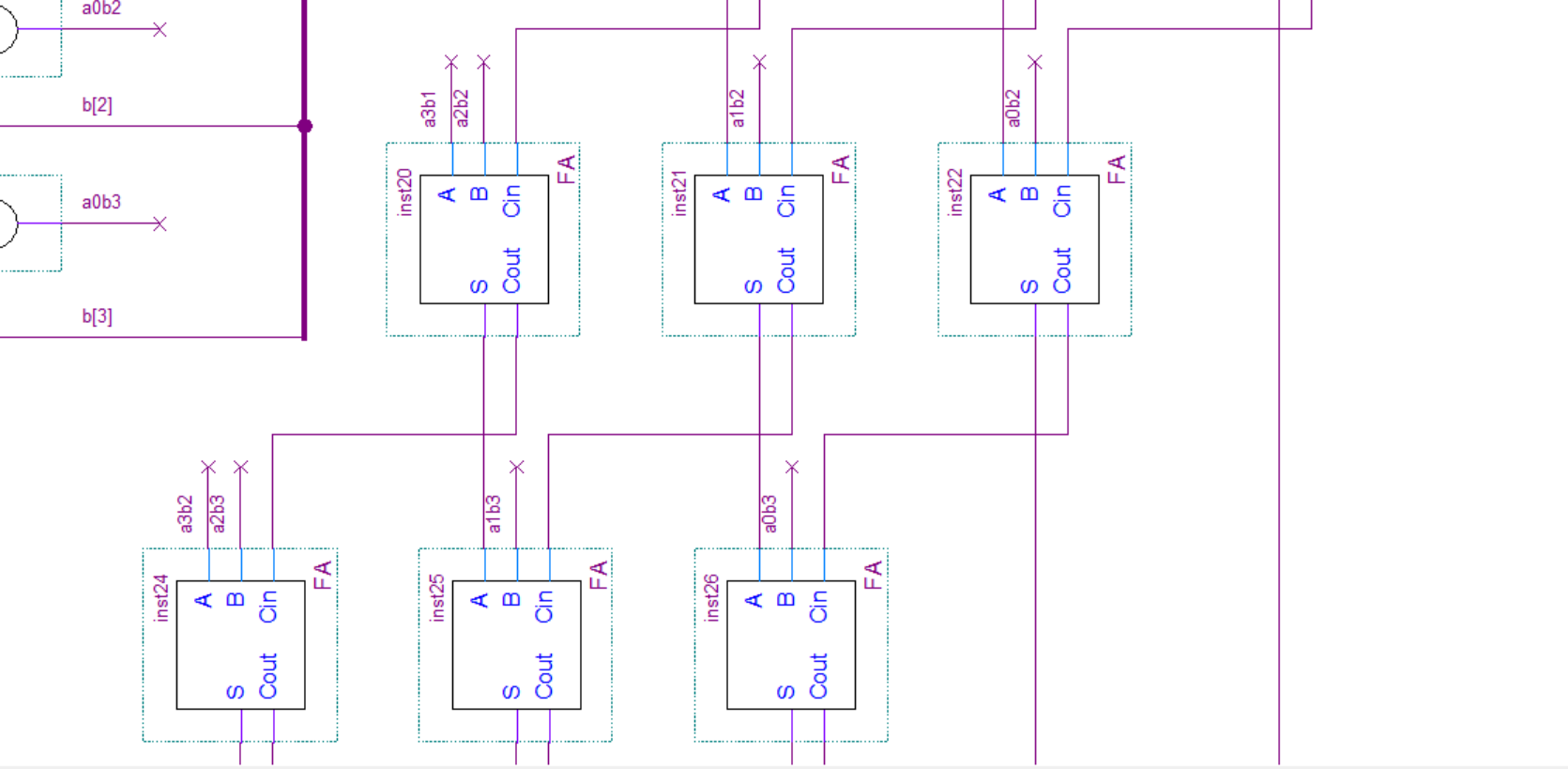

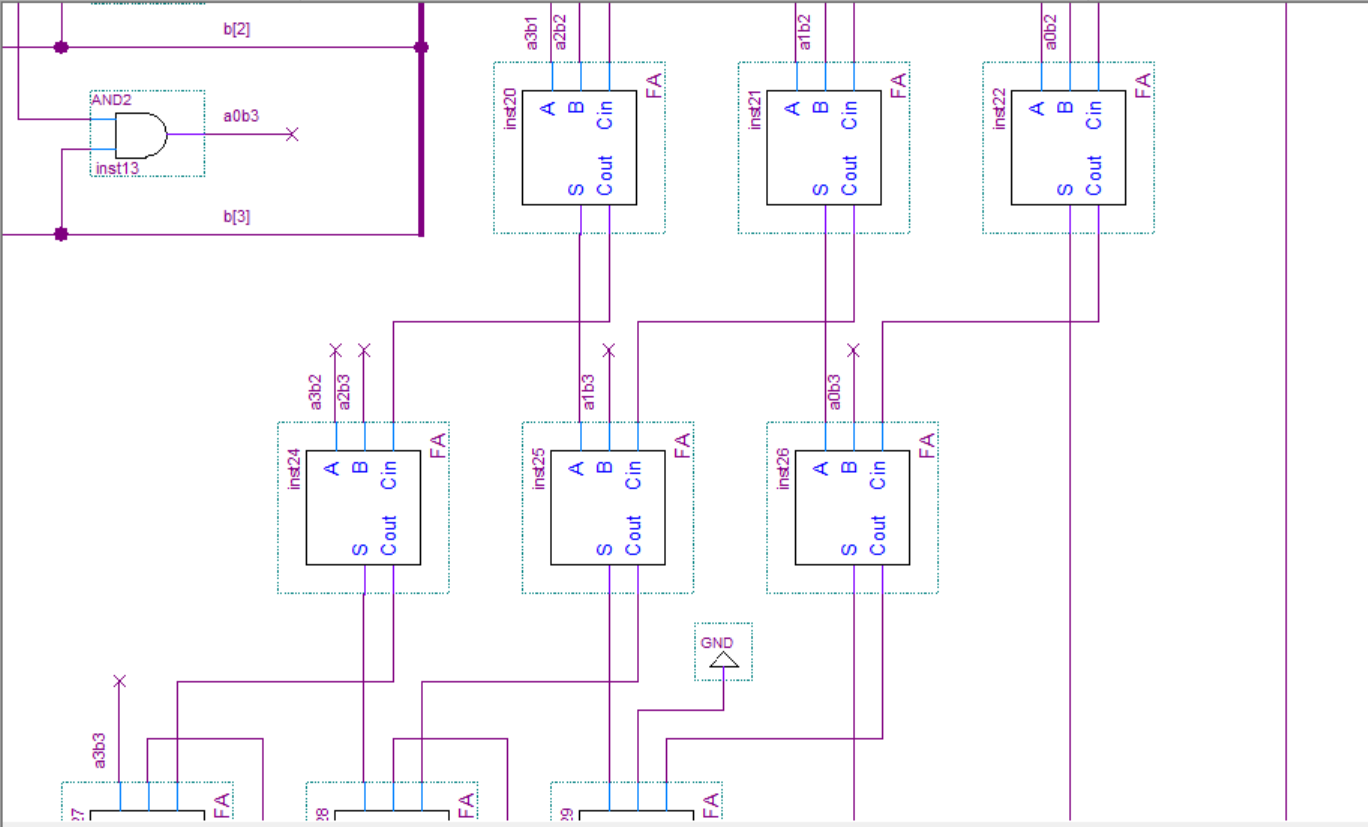

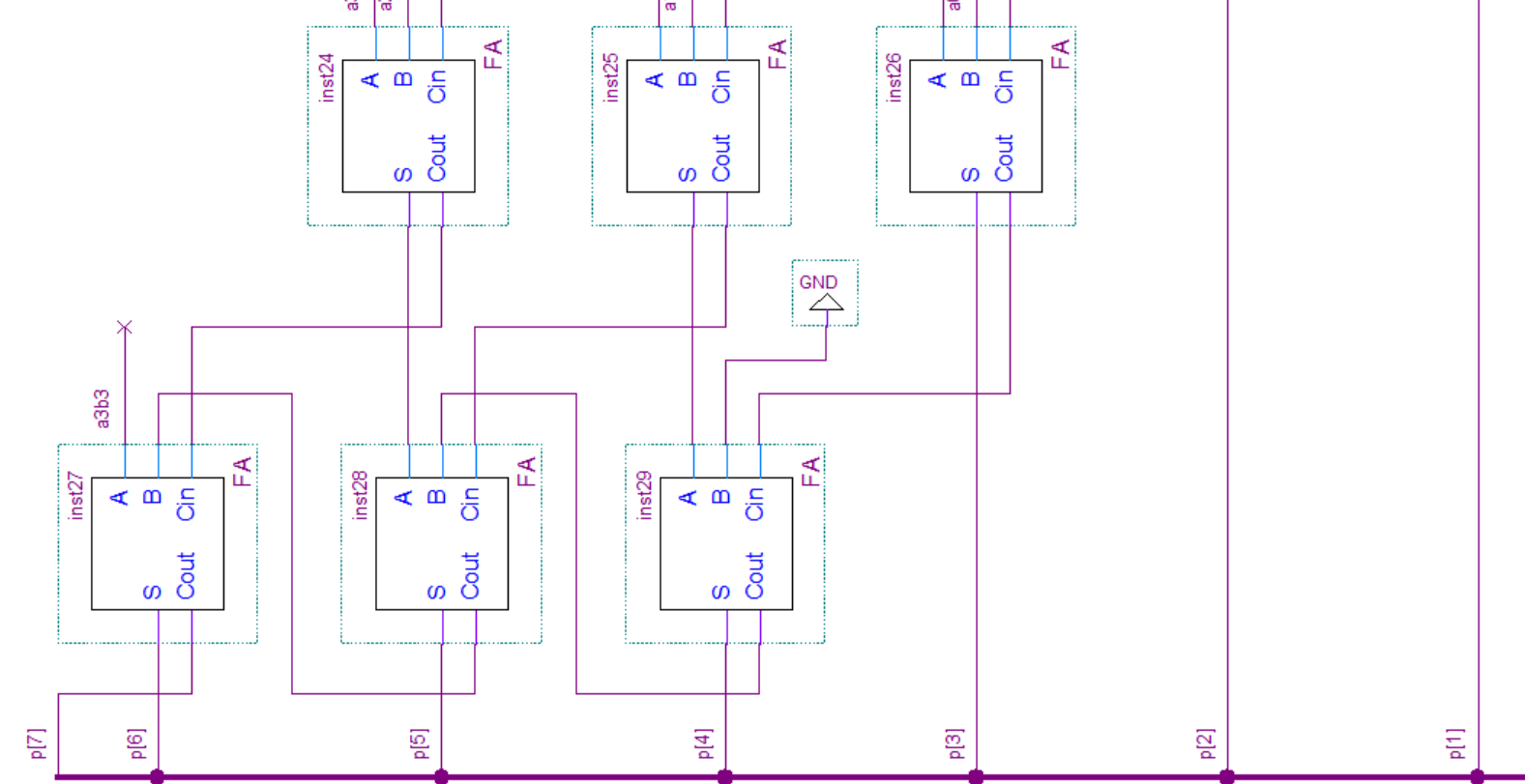

(2)添加元件前,规划好阵列的安排方式,将与阵列、加法器阵列

a. 穿插放

b. 分开放(因为标有相同的标号的线段可视为连接线段,可不必直接相连)

(3)此处选择【b. 分开放】的方式,将与阵列、加法器阵列分开存放

然后通过相同的标号标识连线关系

(4)添加元件:

输入信号input、输出信号output、FA、与门and2、Gnd(对应0)

修改输入信号分别为a[3..0]、b[3..0]

修改输出信号分别为p[7..0]

a. 局部放大:与门阵列部分

b. 上半部分

c. 下半部分

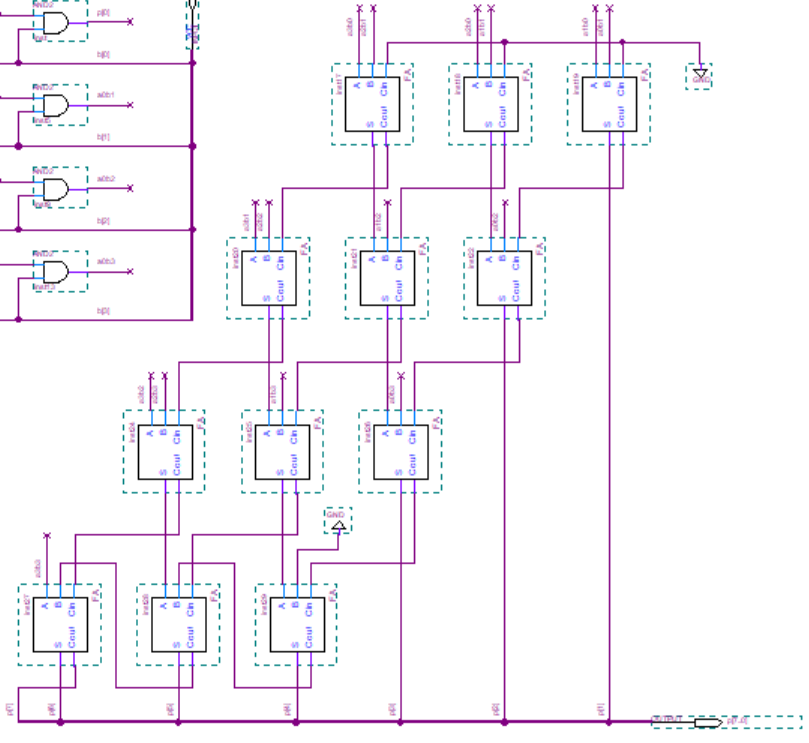

a. 局部放大:加法器阵列部分

b. 上半部分

c. 中间部分

d. 下半部分

(6)连接元件:

连接时为了指定连接的总线中的哪一个信号,需设置连线对应某信号,如:A[0]

(7)编译

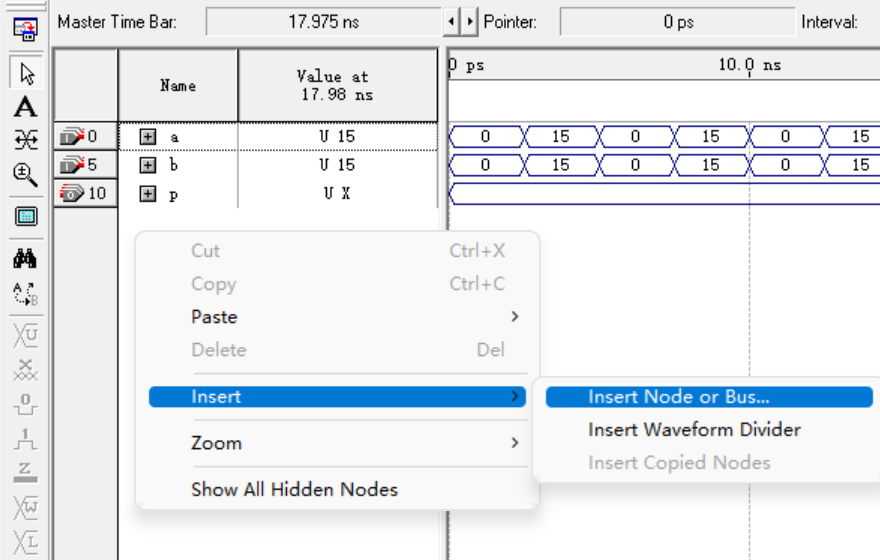

3. 设计仿真波形文件

(1)新建——Vector Waveform File

(2)插入仿真的信号(快捷菜单——inert node or bus——node finder)

a、b、p

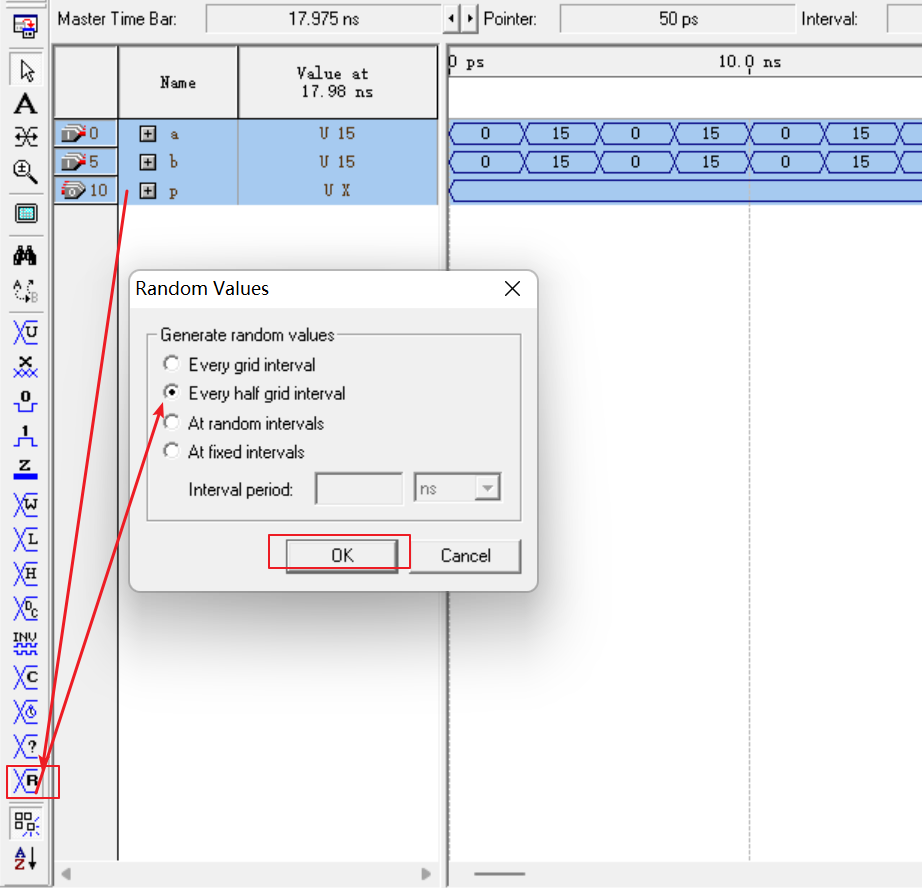

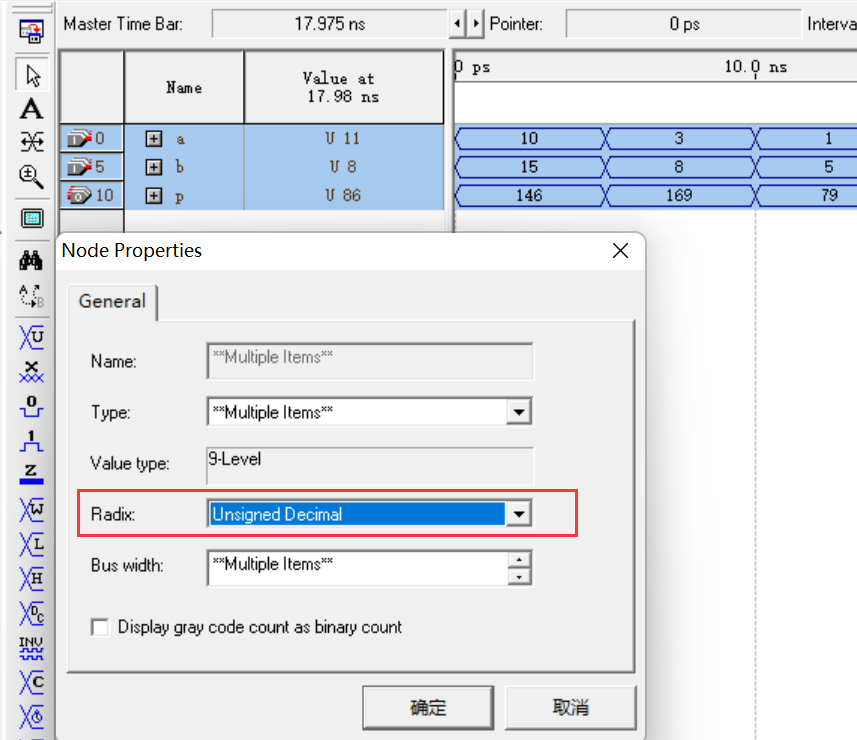

(3)设置a、b均为半个时钟变化一次的随机值

均显示为unsigned Decimal(无符号数)

(4)保存文件——保存为mul.vwf

(5)Processing ——simulation tools 仿真

选择——functional 进行功能仿真,(生成功能仿真的网表文件)

Start——开始仿真

Report——查看仿真结果

4. 用原理图文件mul.bdf,创建symbol文件mul.bsf

(1)文件——Create/Update——Create Symbol File for Current File

三、 建立一个工程,设计5×5带符号的阵列乘法器,并加以仿真

1. 新建工程cmul

(1)保存位置 D:ITQuartuscmul

工程名称 cmul

主文件(top-level design entity)cmul

(2)拷贝FA.bdf、FA.bsf、cmp.bdf、cmp.bsf、mul.bdf、mul.bsf 到 D:ITQuartuscmul

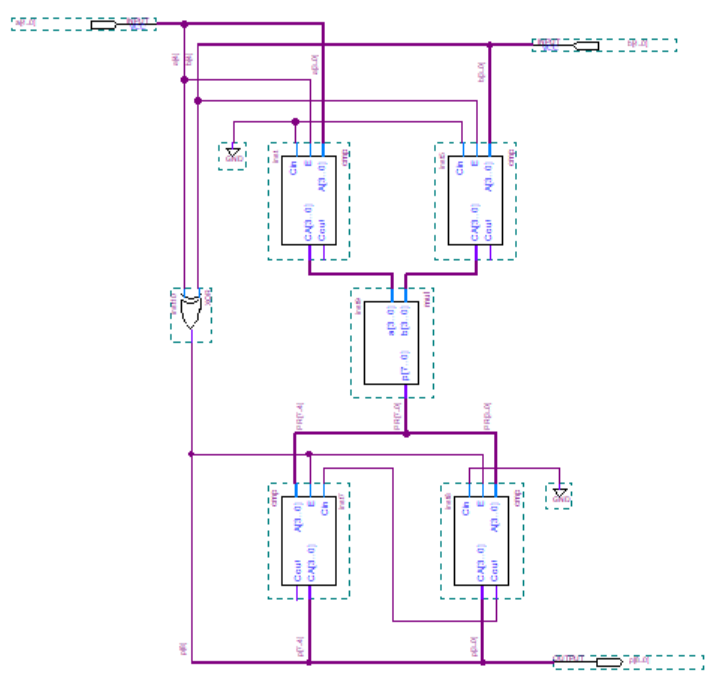

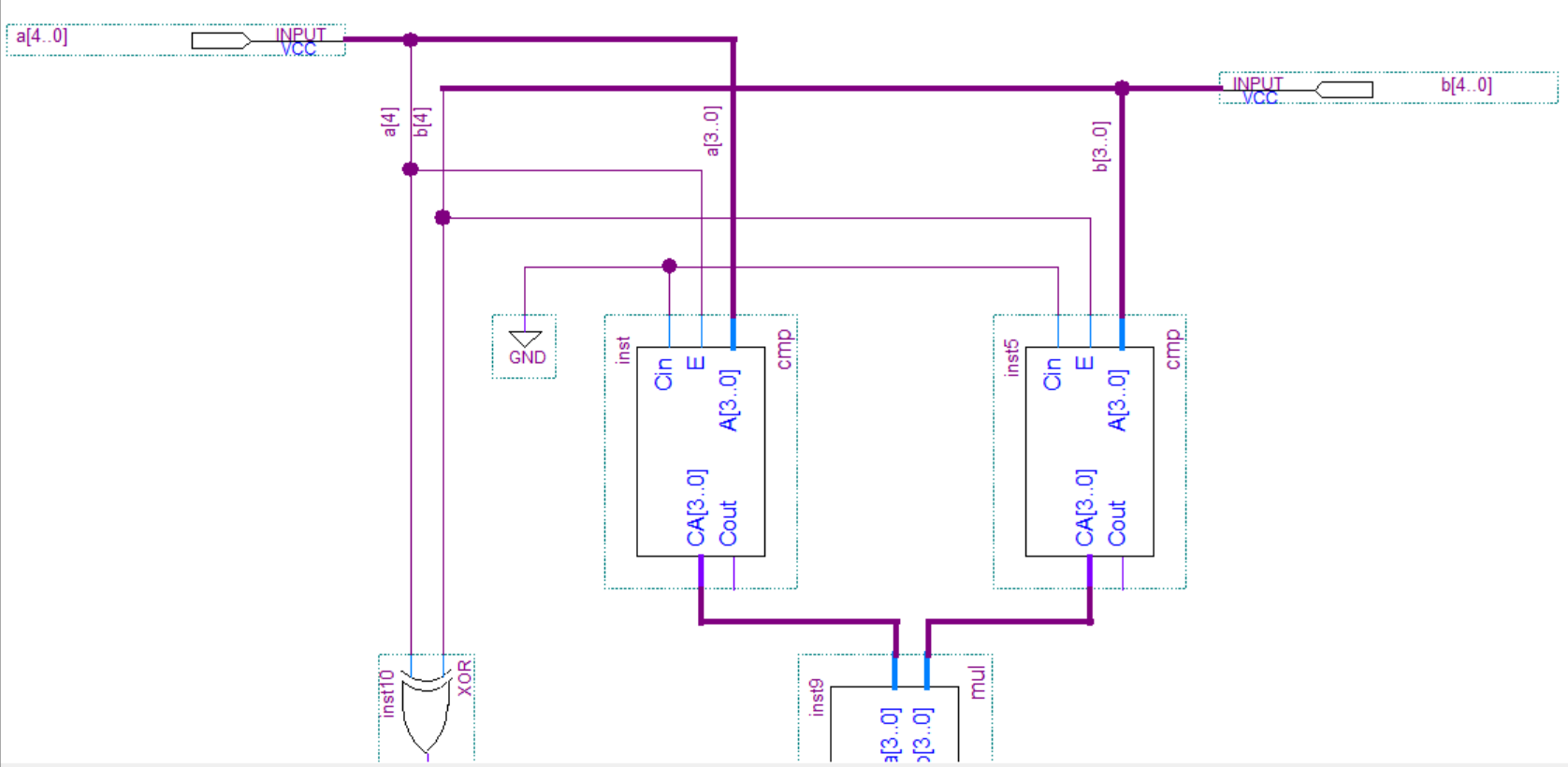

2. 设计原理图文件保存为cmul.bdf

(1)新建——Block Diagram,保存为cmul

(2)添加元件:

输入信号、输出信号、不带符号的4位乘法器、异或门

input output mul xor

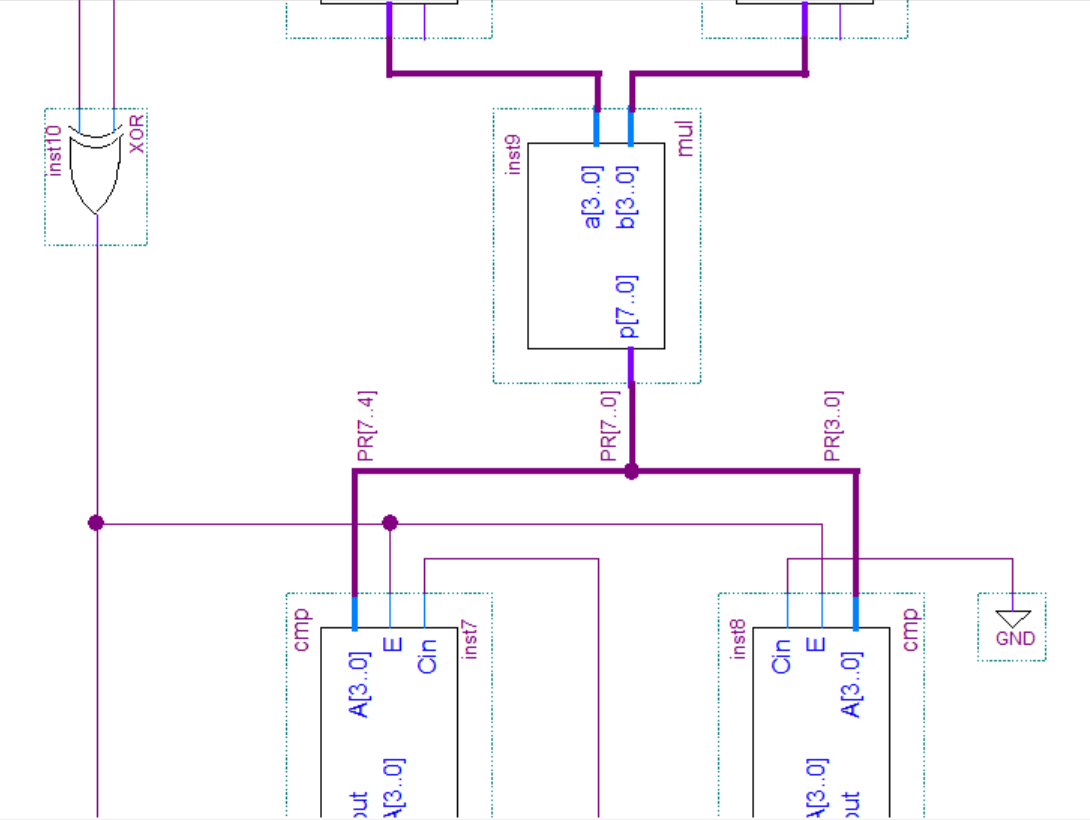

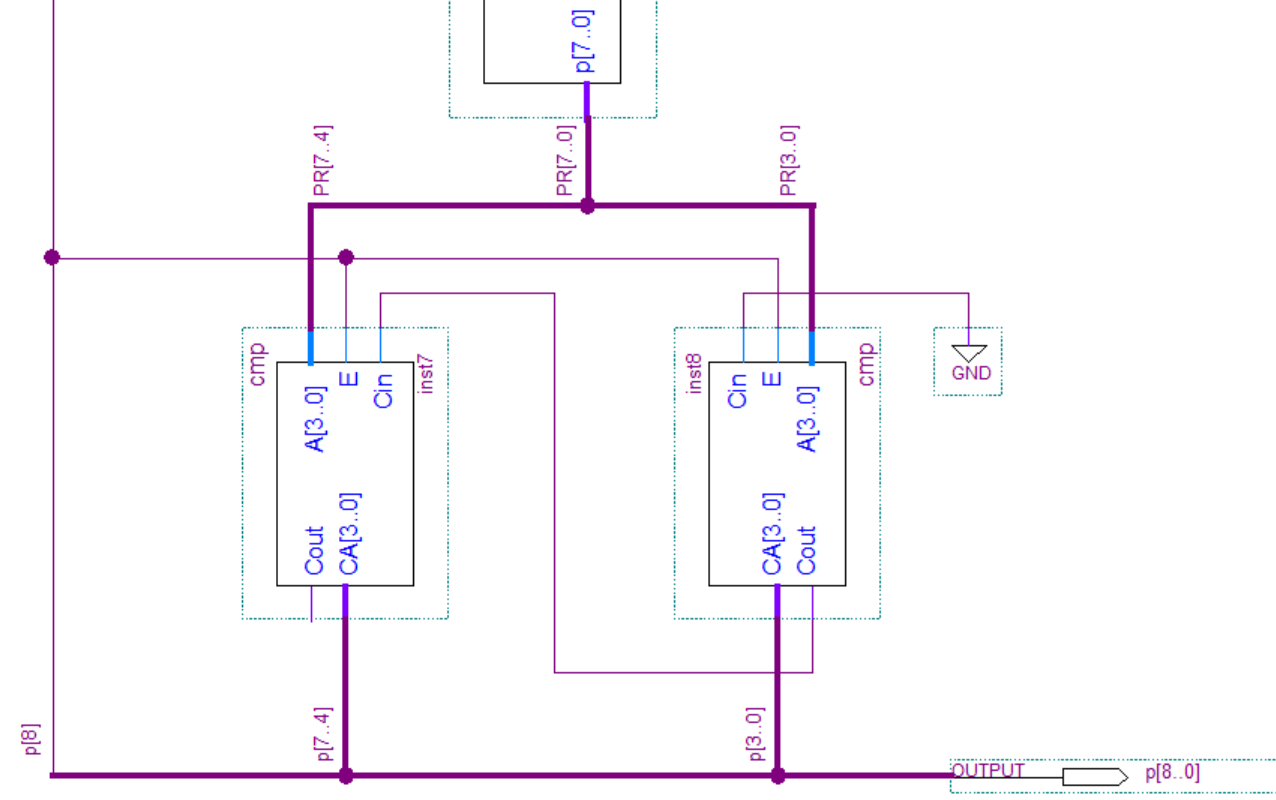

(3)效果图

a. 全局显示

b. 上半部分

c. 中间部分

d. 下半部分

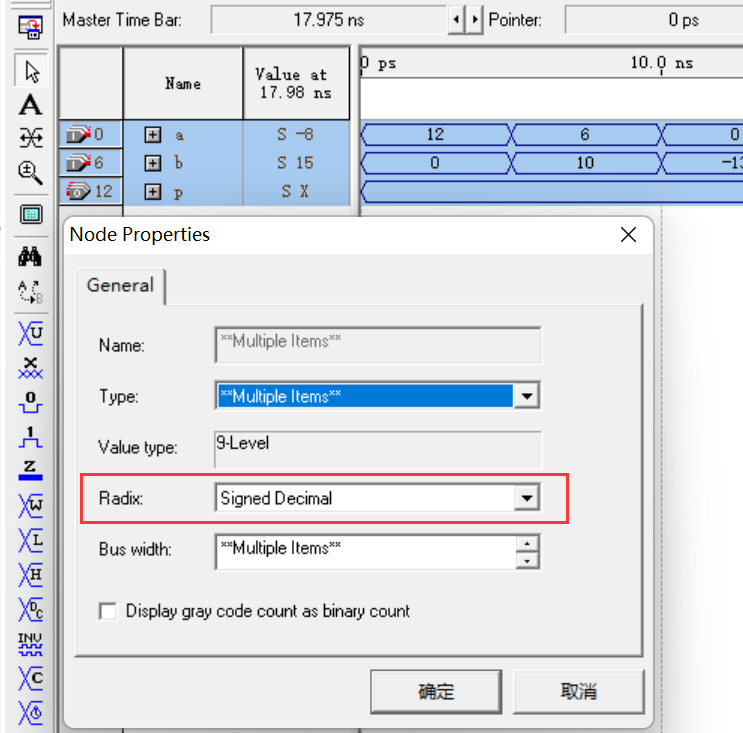

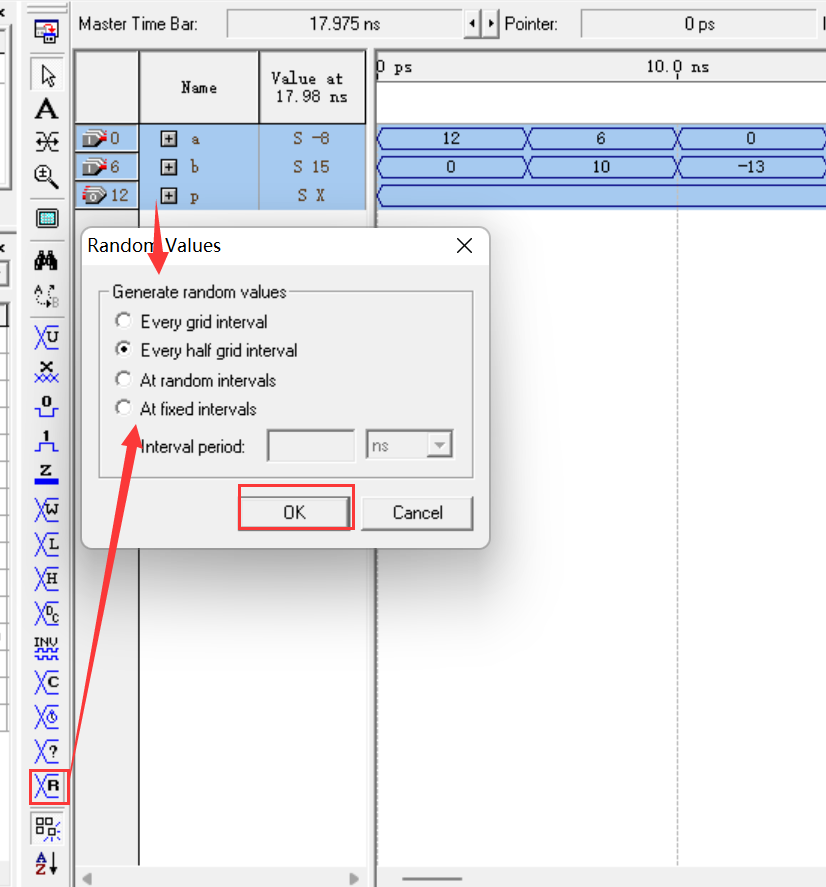

3. 设计仿真波形文件

(1)新建——Vector Waveform File

(2)插入仿真的信号(快捷菜单——inert node or bus——node finder)

a、b、p

(3)a、b、p用有符号数显示

设置a、b为随机数

(4)保存文件——保存为mul.vwf

(5)Processing ——simulation tools 仿真

选择——functional 进行功能仿真,(生成功能仿真的网表文件)

Start——开始仿真

Report——查看仿真结果