在被数电无情折磨了两个日夜之后,我终于使用 Quartus II 以及 FPGA 学习板 V1.4(重邮 光电学院实验中心)做出了 24 小时数字钟,该数字钟拥有如下功能:

基本功能:24 小时计时

拓展功能:时间加速、时间暂停、秒钟滴答声、计时清零

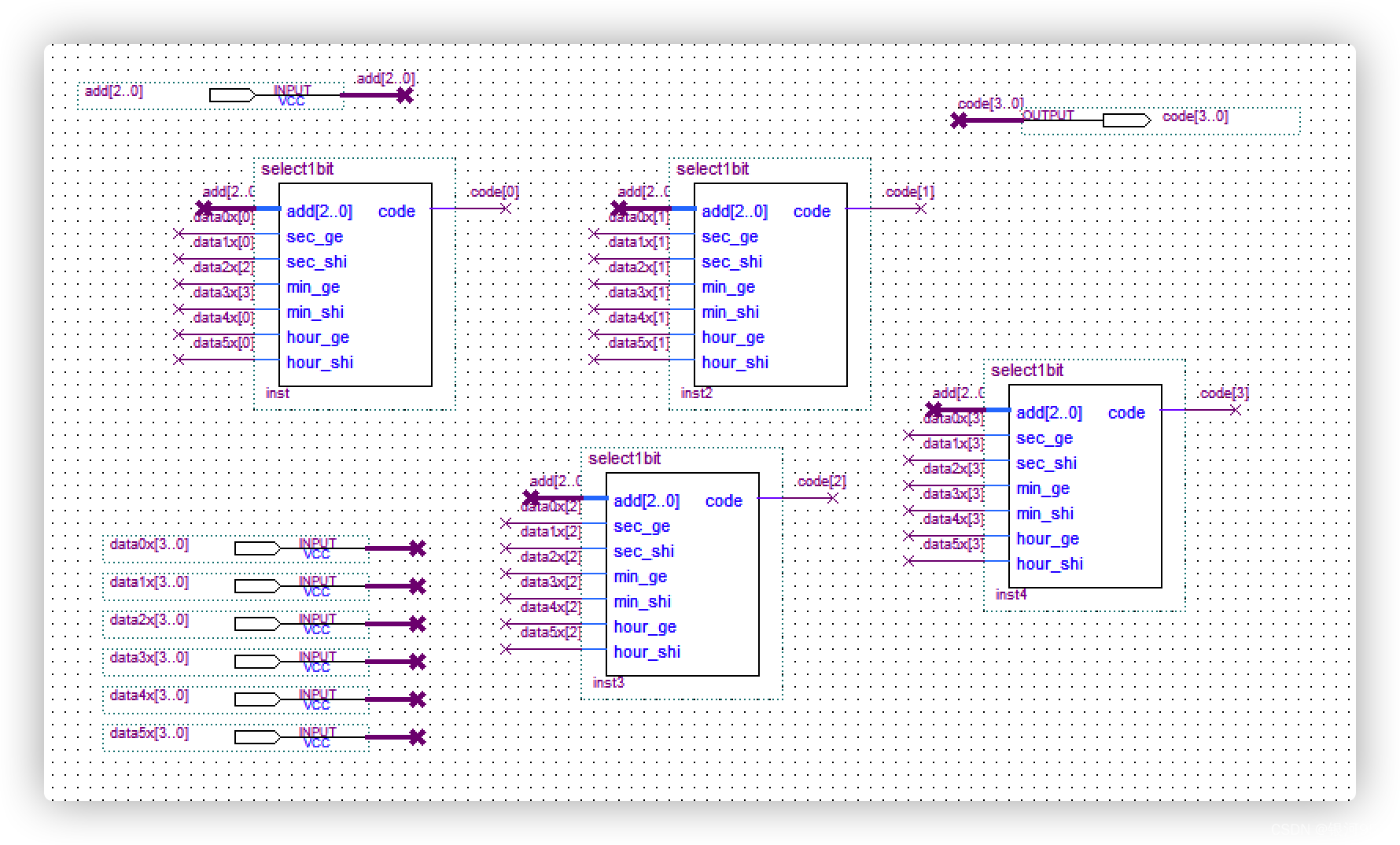

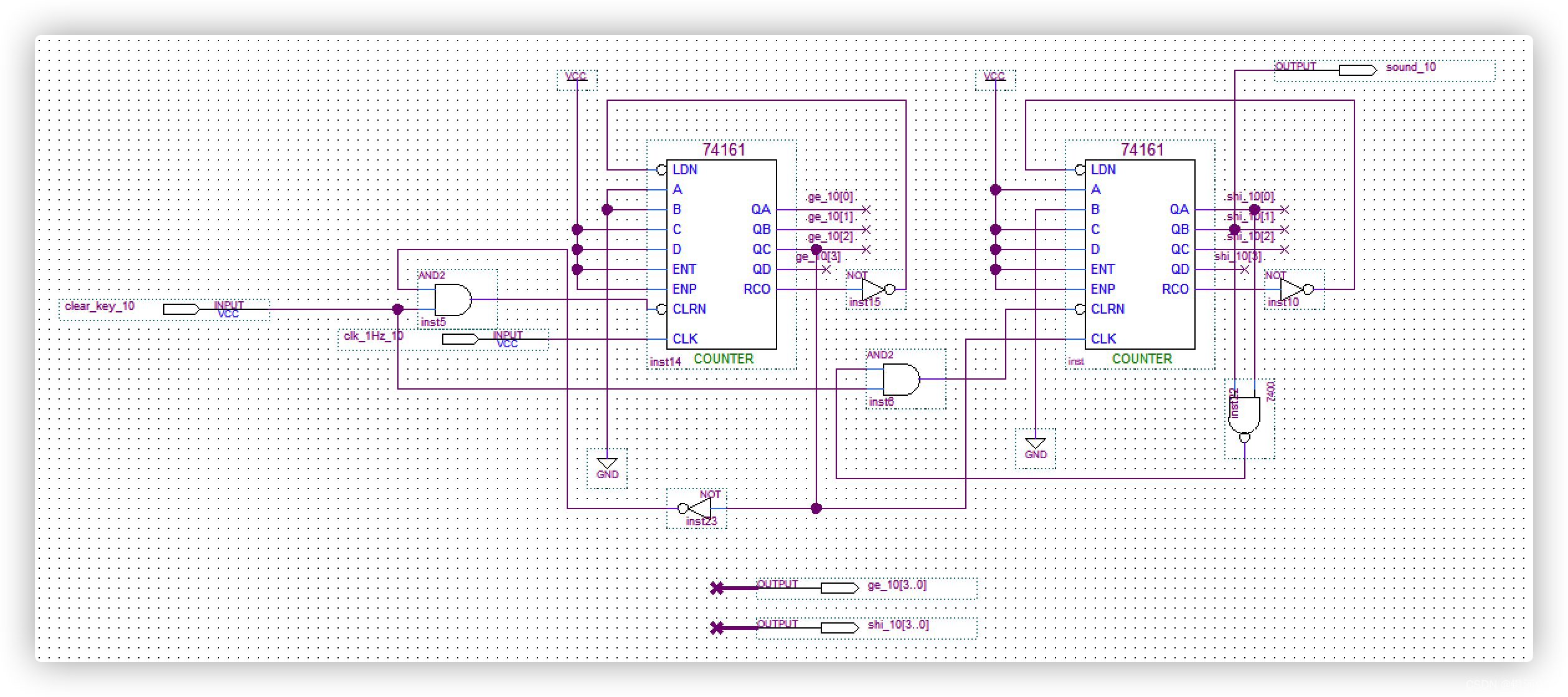

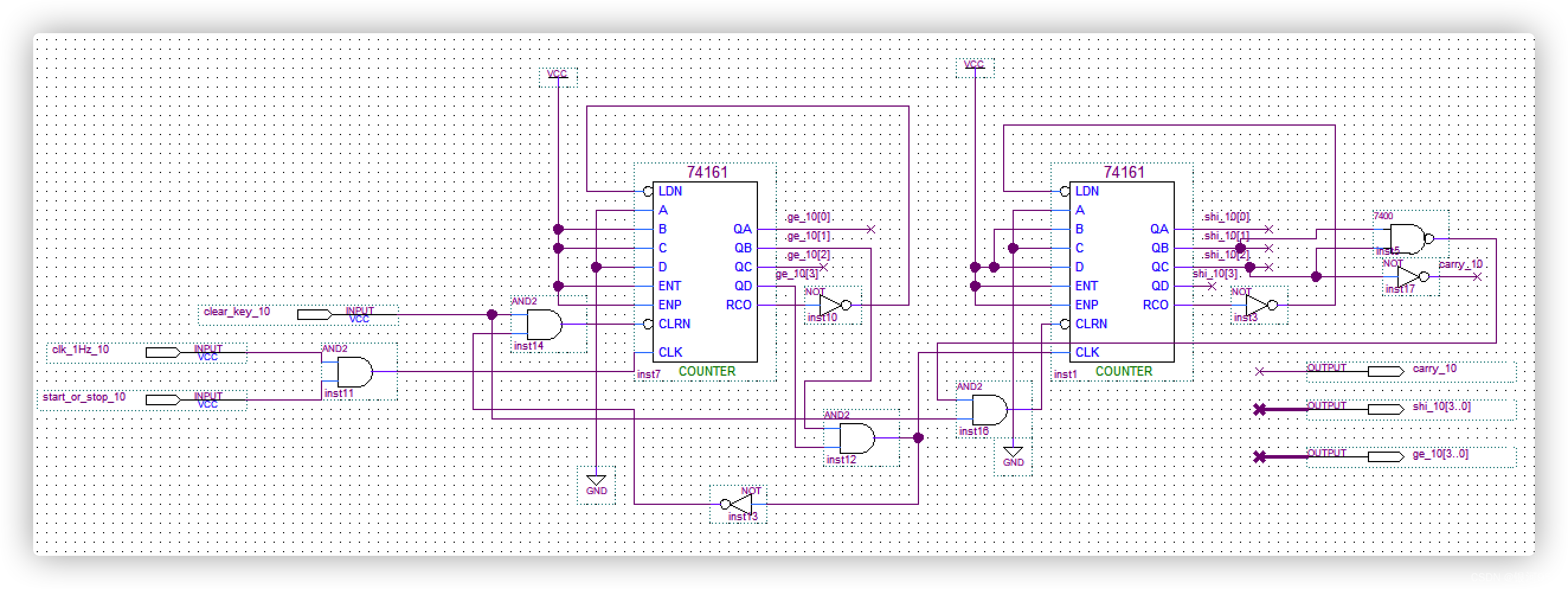

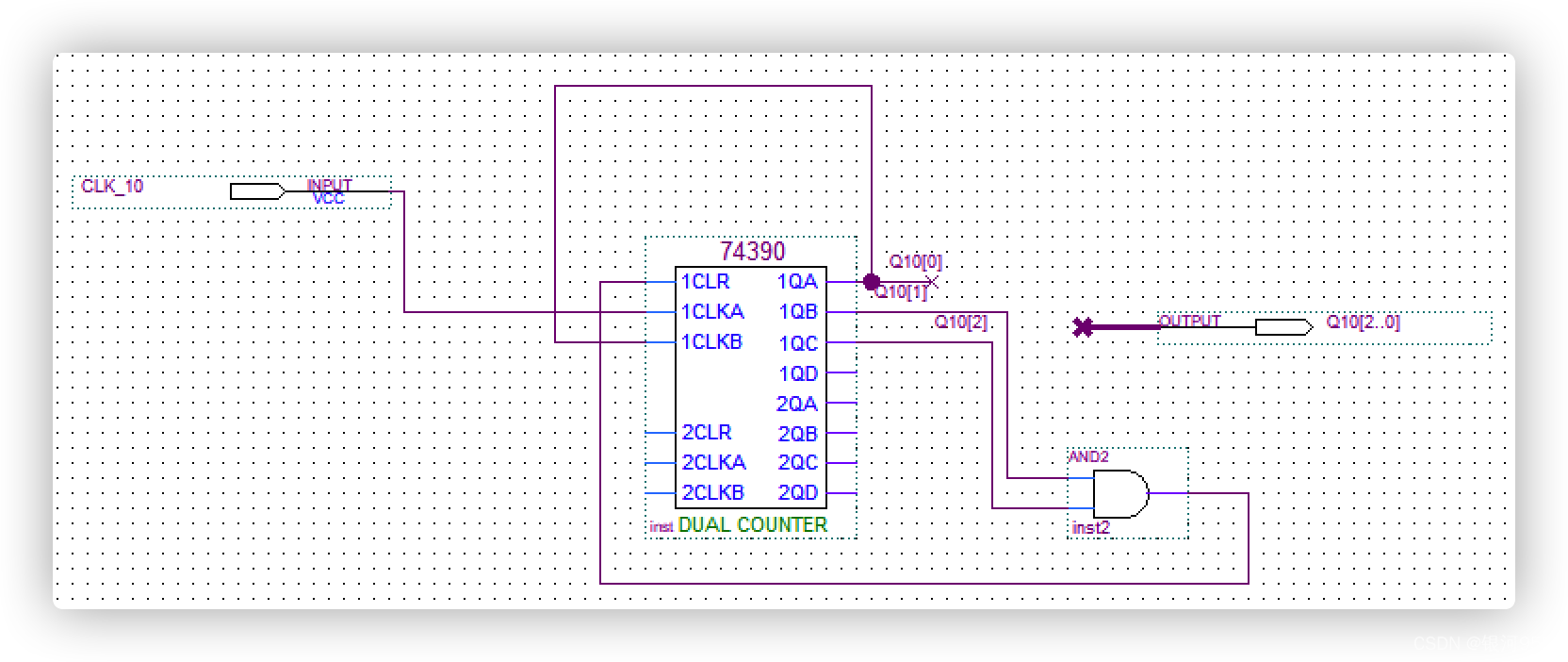

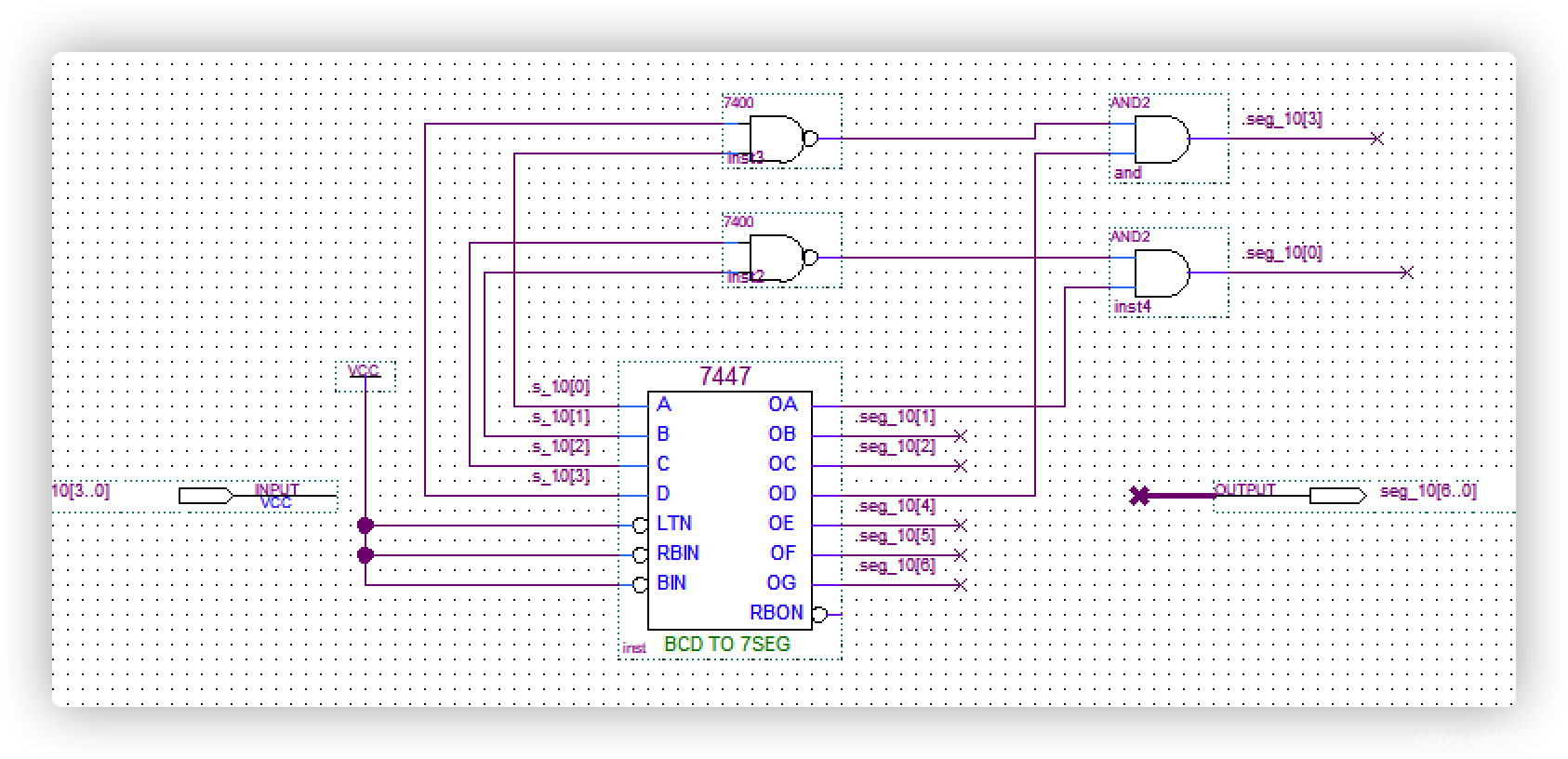

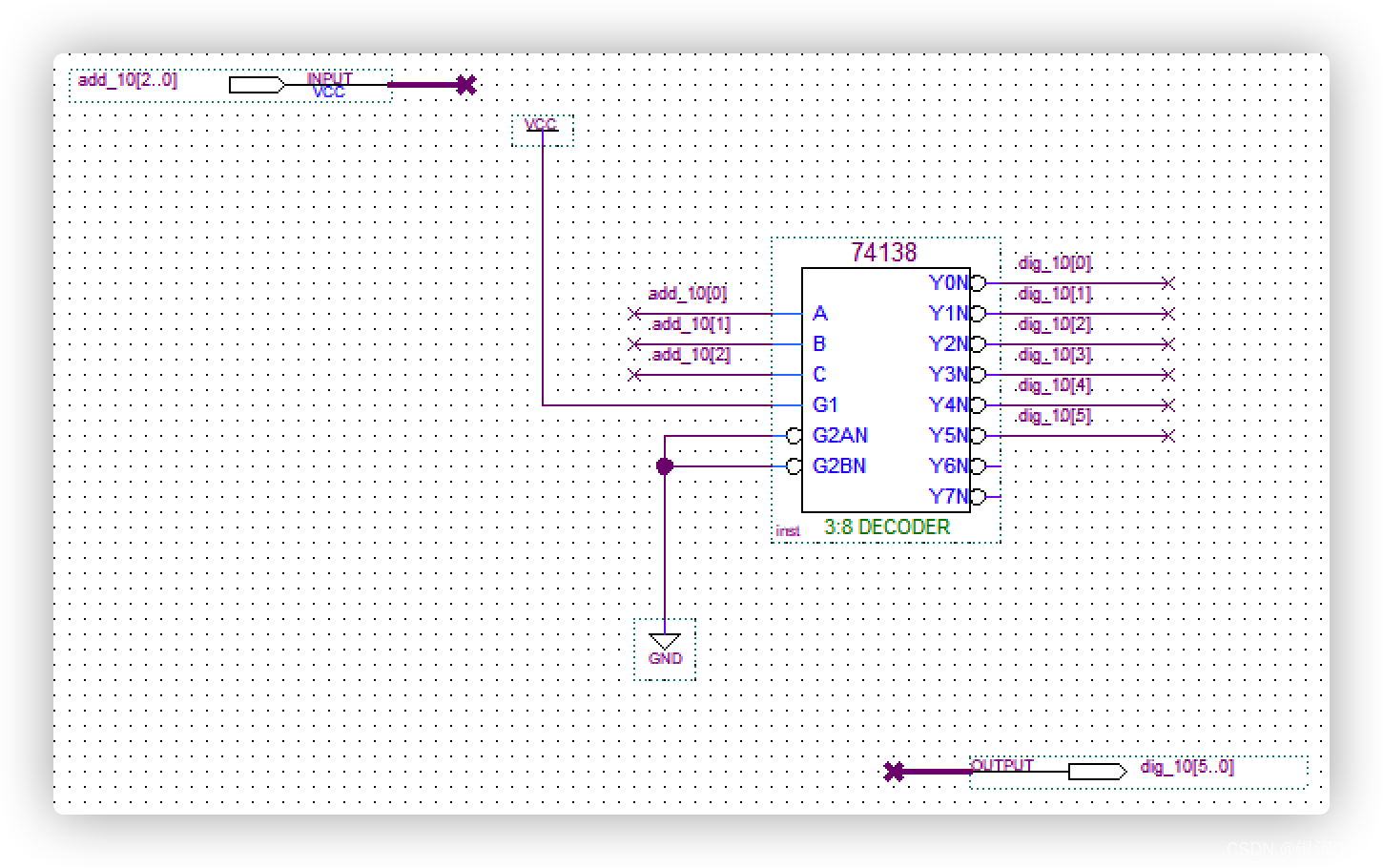

首先是基础功能的实现,基础功能包含 60/24 进制计数模块、译码模块、位选模块、显示模块、分频模块,这些模块均为基础模块,可在《数字电路与逻辑设计 第二版》人民邮电出版社 邹虹 这本书上找到相应的设计方法。其中模 60/24 我是使用的 74161 芯片实现,这里放一下大致的电路图设计情况:

以上的就是这些基础模块的设计电路图,接下来让我们看一下最重要的模 60 以及模 24 的仿真情况。

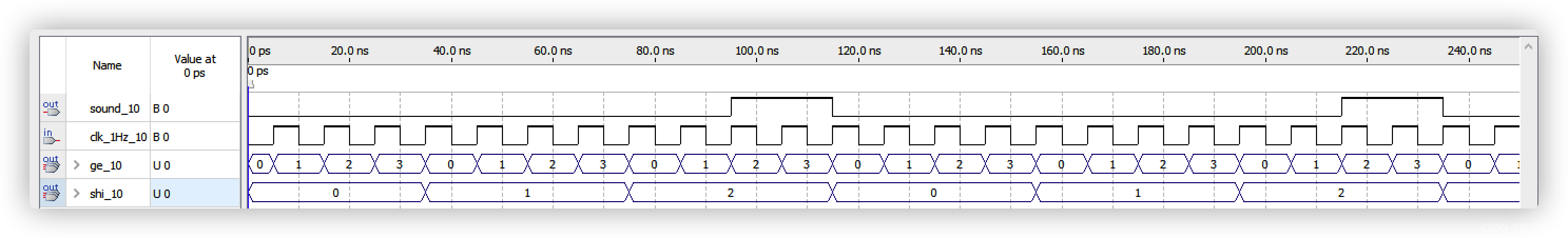

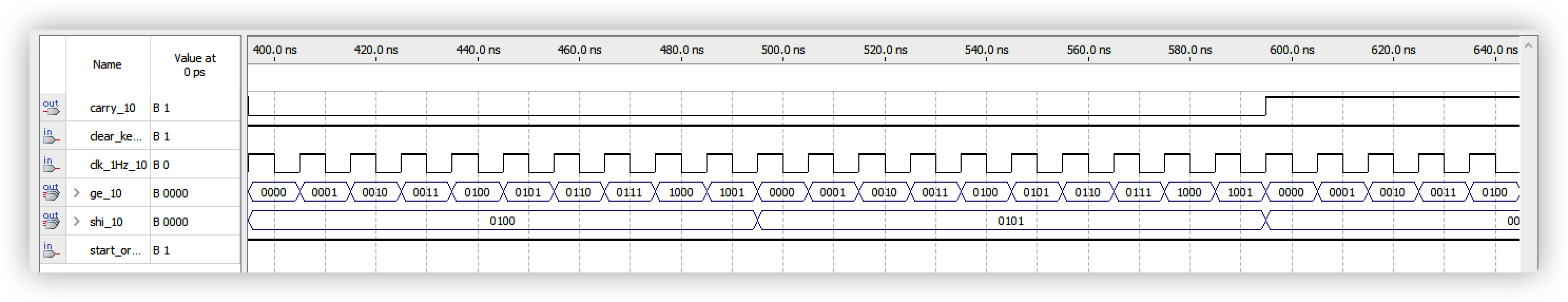

通过波形仿真图可以看到,我是将个位和十位分开做的清零和进位,count 60 部分,个位为 10 进制,十位部分为 6 进制,count 24 部分个位为 5 进制,十位为 3 进制,均使用 74161 芯片实现,这两个模块均有一个 carry 输出,carry 输出为进位信号(59 秒进 1 分,59 分进 1 小时),这样便可以将时、分、秒结合起来,实现数字钟的功能。

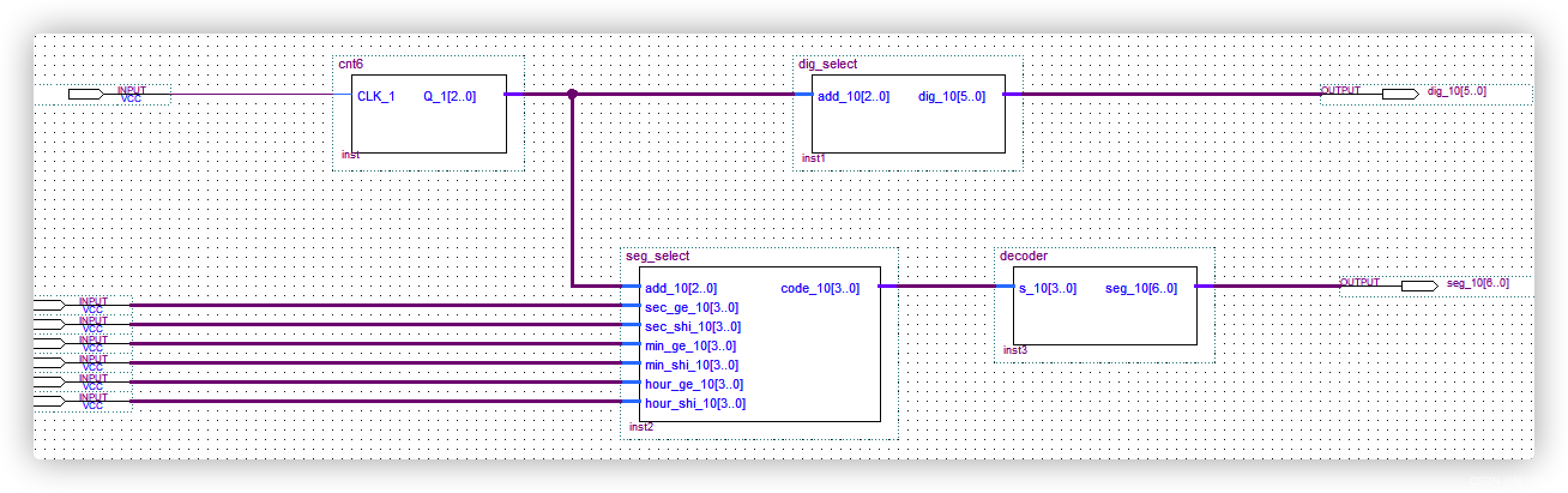

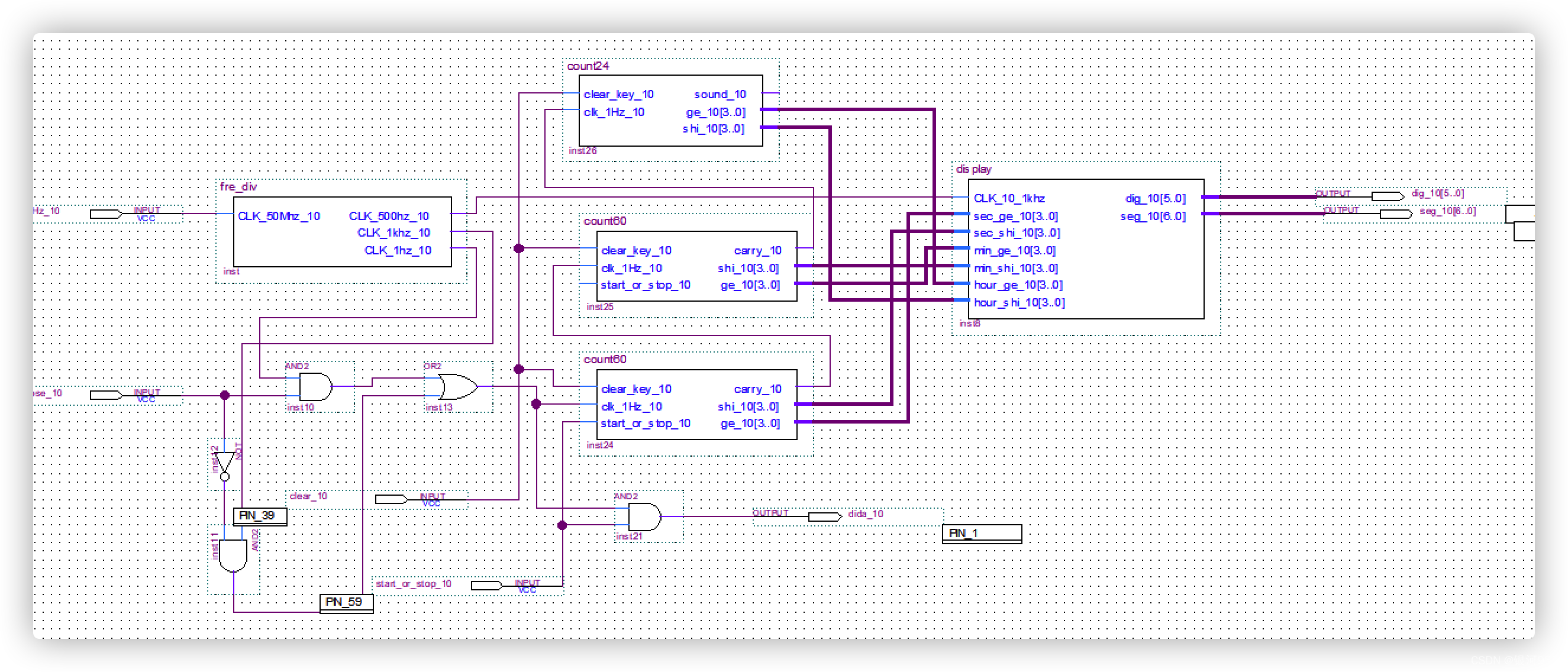

以下为 FPGA 数字钟顶层文件设计电路图:

可以看到数字钟基本实现功能的思路为先将晶振 50MHz 的频率进行分频,分为 1Hz、1kHz 以及 500Hz 的频率,其中 1Hz 时钟信号用来驱动 count 60 模块进行数字钟计数,而 1kHz 和 500Hz 均可以用来驱动显像管显示,只要刷新率高于 1Hz 便可以正常实现显示功能。然后将时、分、秒计数信号输入 display 显示模块进行解码、显示等操作后(display 显示模块的设计电路图在上文中有介绍)最终输出,输出口连接 FPGA 开发板上的阴极管,即可在 FPGA 开发板上实现数字钟基础功能。

基础功能实现完之后我们再来看看拓展功能:

1. 计时滴答声:

将 1Hz 的时钟信号接入到蜂鸣器中,即可实现每秒钟一次“嘀嗒”响声。

2. 时间加速:

我们在分频 50MHz 的时候分出了 1Hz 以及 1kHz 的频率,我们新增一个 input 输入信号绑定一个开关,然后将这个输入信号与 1Hz 信号相与,再将该输入信号的反信号与 1kHz 信号相与,然后将两个信号相或,最终作为时钟信号输入到 count 60 的时钟信号 clk 中来驱动 count 60 模块的工作。如此,便实现了拨动开关控制时间加速的功能。

3. 时间暂停:

我们在 count 60 模块中新增一个输入信号“start or stop”,将该输入信号绑定一个开关,然后将该信号与输入的 1Hz 信号相与输入到 60 进制计数器中,这样我们便成功实现了拨动开关开始/停止计时的功能。

4. 计时清零:

这里用到了 74161 芯片的 CLRN 引脚清零功能,在 count 60、count 24 模块中增加一个输入信号“clear key”,将该信号与 FPGA 开发板上的一个按钮绑定,当按下按钮的时候,该输入信号为 1 ,经过一个非门之后接入到 74161 芯片的 CLRN 引脚上(CLRN 引脚为低电频有效,故需要接一个非门),这样我们便实现了按下按钮清零计时的功能。