文章目录

- 1.SPEC和相关协议

- 2.AHB2APB Bridge 的规格

- 3.AHB2APB Bridge 的interface

- 4.AHB2APB Bridge 的状态机

- 4.1 输入、输出不寄存

- 4.2 输入、输出数据寄存

- 4.3 考虑pslverr反馈传输ERROR时

- 4.4 其他的状态

- 5.AHB2APB读写时序

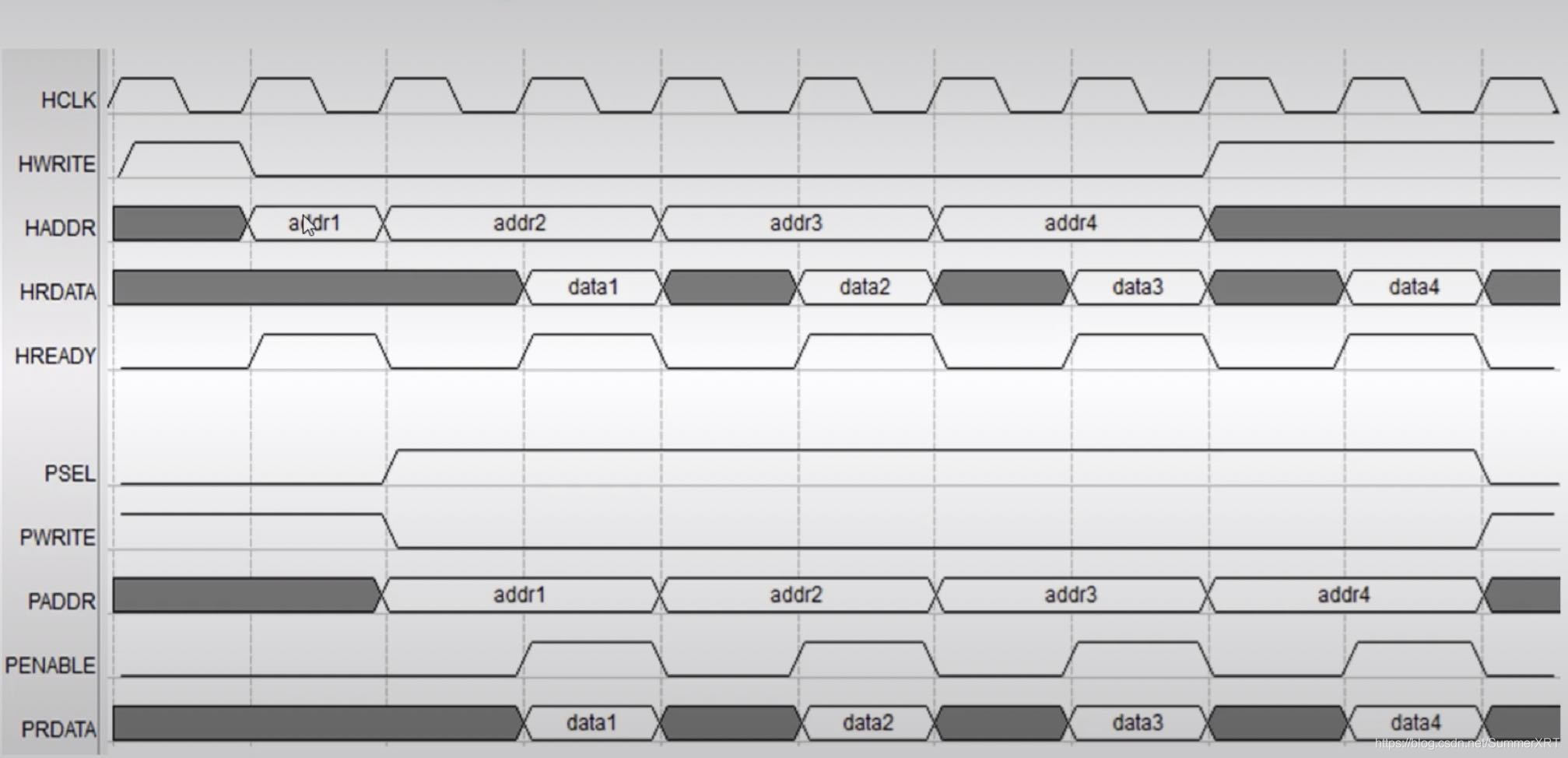

- 读操作

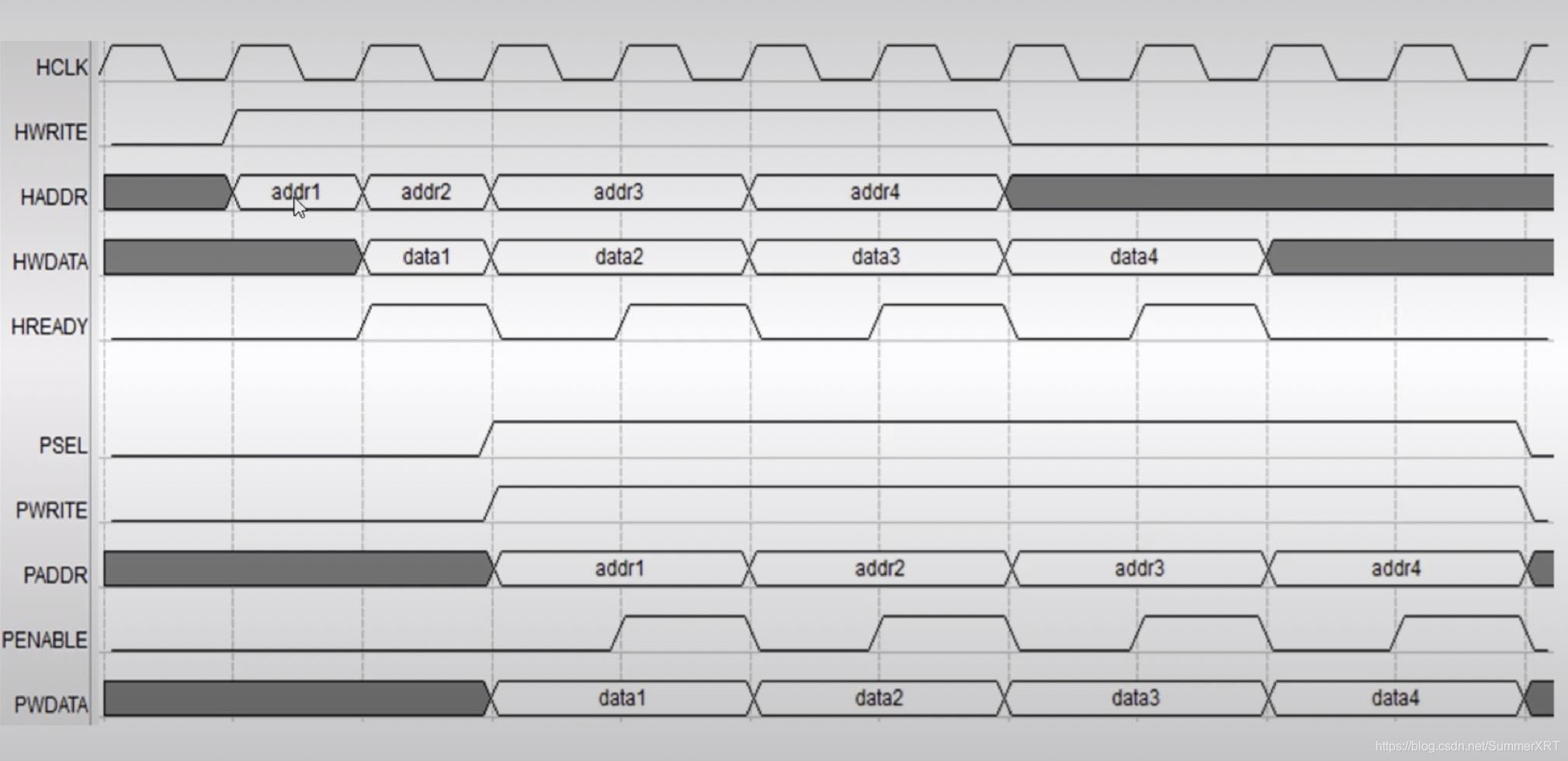

- 写操作

- 6.设计注意事项

- 1.HREADYOUT信号

- 2.Memory Map的边界地址对齐

- 3.Memory Attribute

- 4. ERROR response

- 5.跨时钟域的处理

- 6.采用寄存器寄存一拍

- 7.Verilog设计代码

👉关于AHB2APB的设计的代码请看:AHB2APB同步桥的设计代码

👉关于AHB2APB的验证请看:AHB2APB验证

1.SPEC和相关协议

AHB2APB SPEC请看:ARM官方AHB2APB SPEC

AMBA中文协议请看看:AHB lite协议和APB4协议

ARM AMBA英文原版协议请看:ARM官方文档网址

2.AHB2APB Bridge 的规格

AHB2APB bridge 是完成高性能总线到APB总线的桥接器,主要完成的功能:

- AHB2APB bridge 是APB唯一的master;

- 锁存AHB地址以及控制信号,并使之在整个APB传输期间有效;

- AHB和APB时钟是同步时钟,APB时钟和AHB时钟的分频关系由PCLKEN信号决定;

- 支持一个slave,所以只产生一个选择信号PSEL;

- 对于写传输,驱动数据到APB总线上;对于读传输,驱动APB数据到系统总线上;

- 支持APB模块的使能信号(APBACTIVE);

- 支持输入输出数据寄存或者不寄存,由模块控制参数控制。

- 支持APB总线字节选通信号(pstrb[3:0]),保护控制信号(pprot[3:0])。

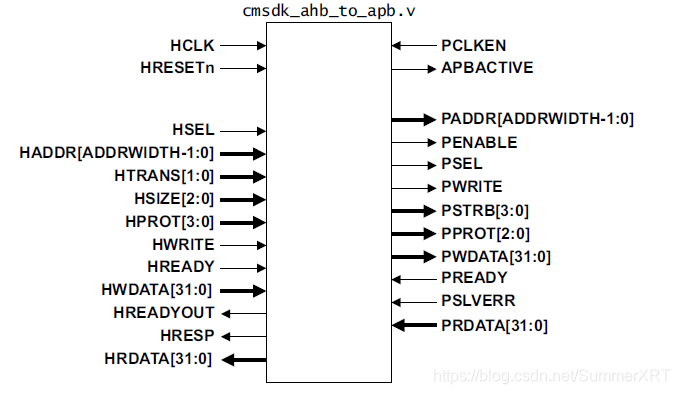

3.AHB2APB Bridge 的interface

- 需要一个AHB 的 interface,定义AHB的接口信号和方向 ;

- 需要一个APB 的interface;

4.AHB2APB Bridge 的状态机

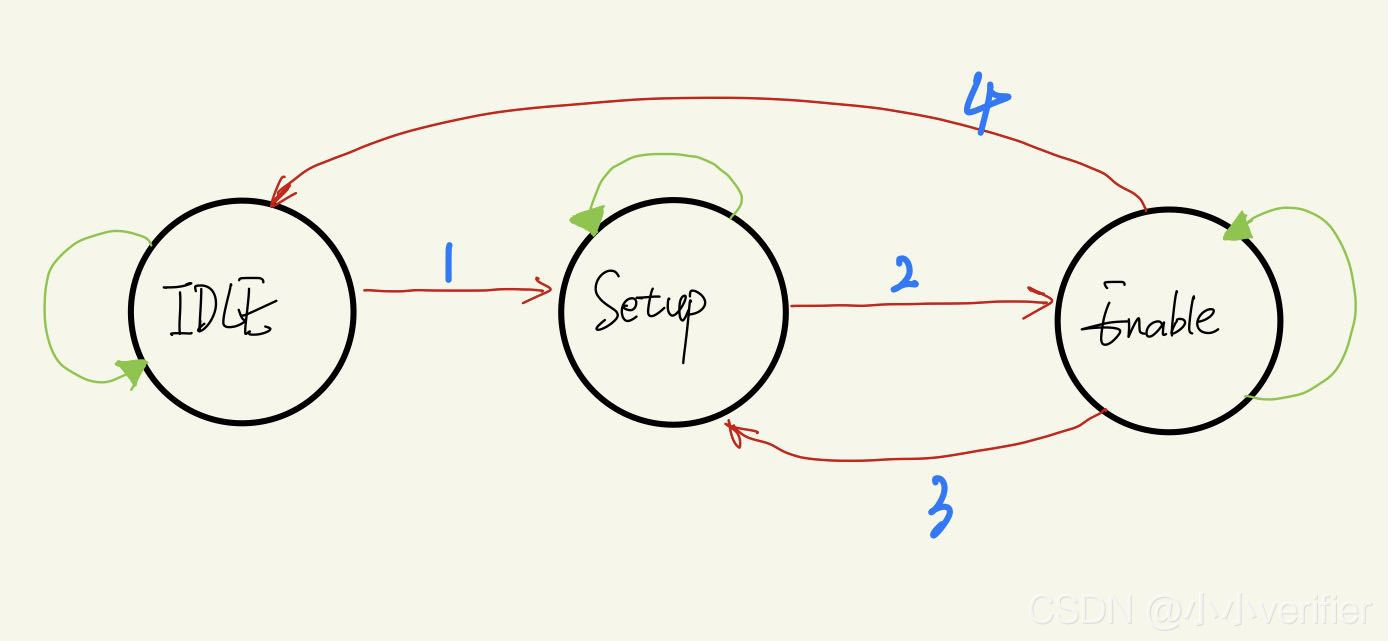

4.1 输入、输出不寄存

此状态机:

- 输入(wdata)、输出数据(rdata)均不需要寄存一拍;

- 不考虑 pslverr 情况;

这种情况与APB状态机是一样的,如下图所示:

注:图中的绿色箭头为状态机的 else 情况,防止出现死锁。

| 状态 | 描述 |

|---|---|

| IDLE | 传输空闲状态,为总线的默认状态 |

| SETUP | 传输建立状态 |

| ENABLE | 传输状态 |

解释上图中的状态转移:

注:PCLKEN为产生APB时钟的分频信号;apb_select 为传输建立的选通信号;状态跳转发生在HCLK的上升沿。

| 当前状态 | 次态路径 | 描述 | 满足条件 |

|---|---|---|---|

| IDLE | 1 | 当收到AHB的传输请求时,会先将apb_select拉高,状态跳转到SETUP状态 ;否则PCLKEN未有效之前,保持在IDLE状态 | apb_select |

| SETUP | 2 | 当APB的时钟上升沿到来时(PCLKEN有效),将PENABLE信号拉高 ;否则PCLKEN未有效之前,保持在SETUP状态 | PCLKEN |

| ENABLE | 3 | 如果紧跟着仍然还有传输(PREADY & apb_select),状态又跳转回SETUP ;否则PCLKEN未有效之前,保持在ENABLE状态 | PREADY & apb_select & PCLKEN |

| ENABEL | 4 | 如果紧跟着后面没有传输, 则跳回IDLE状态 | PREADY & (! apb_select) & PCLKEN,即else if(! apb_select) |

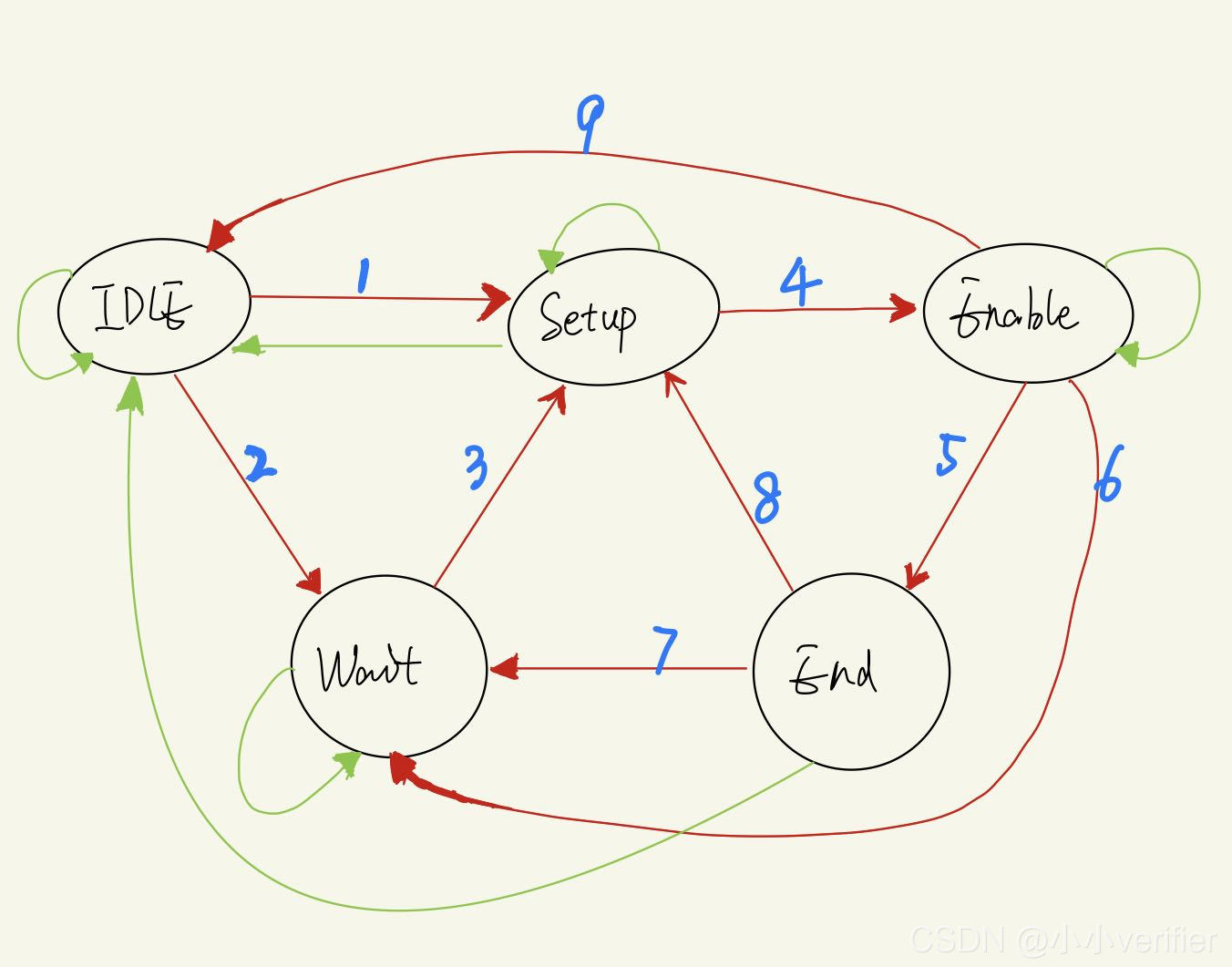

4.2 输入、输出数据寄存

此状态机:

- 输入、输出数据均寄存一拍;

- 但不考虑 pslverr 情况;

注:图中的绿色箭头为状态机的 else 情况,防止出现死锁。图中有一处错误:setup状态有一个绿色箭头指向IDLE状态,这个路径是不存在的。

在原有输入输出数据不寄存的基础上,插入两个状态:

- ST_APB_WAIT

- ST_APB_ENDOK

| 状态 | 描述 |

|---|---|

| IDLE | 传输空闲状态,为总线的默认状态 |

| WAIT | 传输等待状态,将输入和输出数据寄存一拍 |

| SETUP | 传输建立状态 |

| ENABLE | 传输状态 |

| END | 传输结束状态。因为输出要寄存一拍 |

解释上图的跳转条件:

注:reg_wdata_cfg和reg_rdata_cfg分别是否需要寄存输入、输出数据的控制信号。

| 当前状态 | 次态路径 | 描述 | 满足条件 |

|---|---|---|---|

| IDLE | 1 | 当APB时钟时钟上升沿到来时(PCLKEN有效);并且apb_select为高;并且 只要是满足读操作或者写数据不需要寄存,就跳转到SETUP状态 ;否则继续保持IDLE状态 | PCLKEN & apb_select & (~(reg_wdata_cfg & HWRITE) ) |

| IDLE | 2 | 如果条件1不符号(也就是数据需要寄存一拍),并且apb_select为高时 ,就将状态跳转到 wait 状态 ;否则继续保持IDLE状态 | PCLKEN & apb_select & reg_wdata_cfg & HWRITE ;相当于else if(apb_select) |

| WAIT | 3 | 如果APB时钟上升沿到来,就将状态跳转到SETUP状态,否则继续保持WAIT状态 | PCLKEN |

| SETUP | 4 | 如果APB时钟上升沿到来,就将状态跳转到ENABLE状态,否则继续保持setup状态 | PCLKEN |

| ENABLE | 5 | 如果APB时钟上升沿到来 ,PREADY为高,并且输出数据rdata需要寄存,则跳转到END状态;否则保持在ENABLE状态 | PREADY & PLKEN & reg_rdata_cfg |

| ENABLE | 6 | 当APB时钟上升沿到来,如果输出数据不需要寄存一拍,并且没有后续传输进行,则跳转到 WAIT 状态 | PREADY & PLKEN & (! reg_rdata_cfg) & ( ! apb_select) |

| END | 7 | 当APB时钟上升沿到来 ,并且仍然有后续传输(PCLKEN & apb_select ),并且如果输入数据需要寄存一拍,则跳转到WAIT状态 ; ;如果7、8路径条件均不符合,则跳转回IDLE状态 | PCLKEN & apb_select ®_wdata_cfg & HWRITE |

| END | 8 | 当APB时钟上升沿到来 ,并且仍然有后续传输(PCLKEN & apb_select ),如果输入数据不需要寄存,则跳转到SETUP状态 ;如果7、8路径条件均不符合,则跳转回IDLE状态 | PCLKEN & apb_select & ~(reg_wdata_cfg & HWRITE) |

| ENABLE | 10 | 如果输出数据不需要寄存器,并且紧跟着还有传输进行,则跳转到 IDLE 状态 | PREADY & PLKEN & (~reg_rdata_cfg) & apb_select |

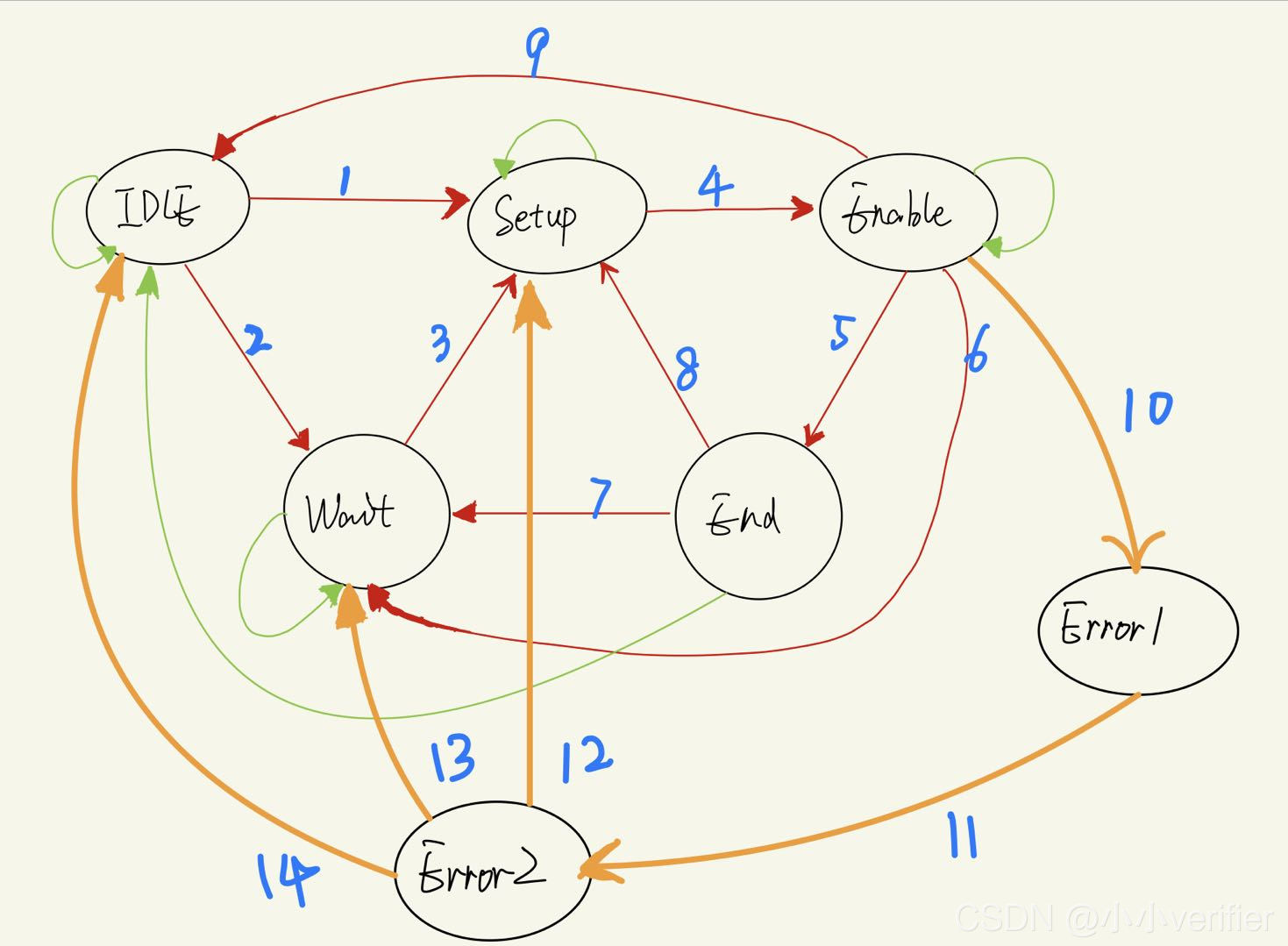

4.3 考虑pslverr反馈传输ERROR时

此状态机:

- 输入、输出数据均寄存一拍;

- 并且向AHB master 反馈 HRESP 信号;

注:上图中的黄色的路径为新增ERROR响应后的状态转移。因为AHB master要想接收到slave反馈回来的error信号,这个error信号必须要保持两拍,需要再加入两个传输错误状态:

- ERROR1

- ERROR2

| 状态 | 描述 |

|---|---|

| ERROR1 | 传输ERROR状态1,MASTER 可以判断是取消burst,还是继续传输 |

| ERROR2 | 传输ERROR状态2,根据master做出相应处理后,根据总线状态判断后续状态机的次态 |

注:其他路径与第二种状态机一样,为了文章不啰嗦,直接写后续的新增的状态跳转路径

| 当前状态 | 次态路径 | 描述 | 满足条件 |

|---|---|---|---|

| ENABLE | 10 | 如果 PSLVERR 拉高,则进入 ERROR1 状态,否则,开始判断是否满足5、6、9的条件 | PREADY & PSLVERR & PCLKEN |

| ERROR1 | 11 | 下一个 HCLK 上升沿到来就直接跳转到ERROR2状态 | |

| ERROR2 | 12 | 如果还有传输继续,并且输入数据不需要寄存,就跳转到 SETUP 状态 | PCLKEN & apb_select & !(reg_wdata_cfg & HWRITE) |

| ERROR2 | 13 | 如果还有传输继续,并且写入的数据需要寄存,就跳转到 WAIT 状态 | PCLKEN & apb_select ®_wdata_cfg & HWRITE |

| ERROR2 | 14 | 如果没有传输继续,就直接跳转到 IDLE 状态 | PCLKEN & ! apb_select |

4.4 其他的状态

- 读数据寄存,写数据不寄存时,并且存在或不存在pslverr的情况;

- 写数据寄存,读数据不寄存时,并且存在或不存在pslverr的情况;

5.AHB2APB读写时序

读操作

写操作

6.设计注意事项

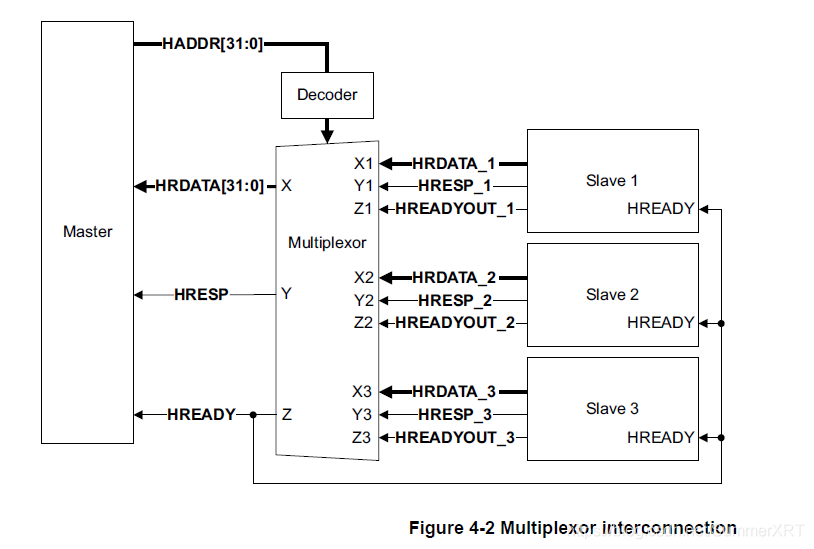

1.HREADYOUT信号

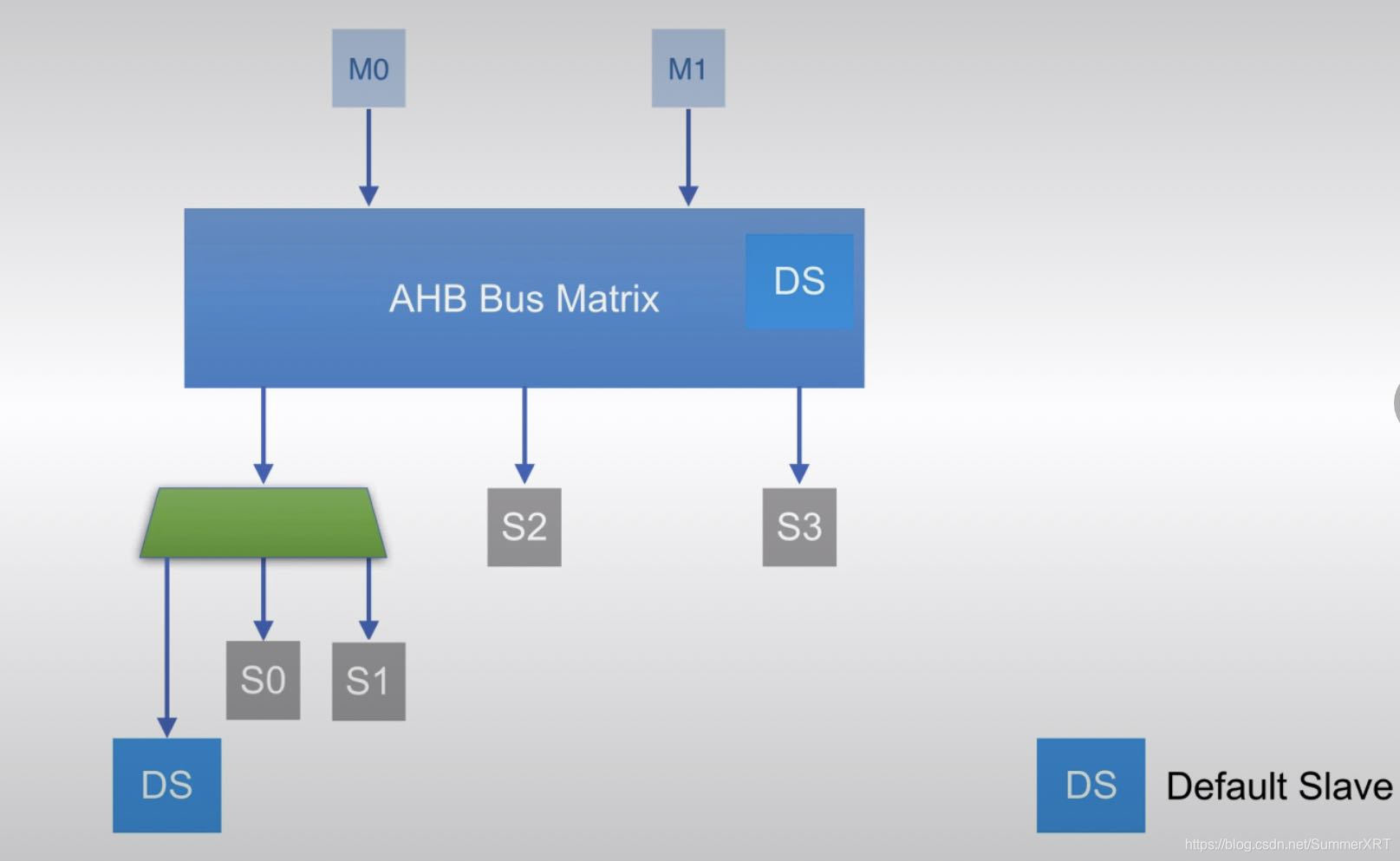

从下图我们可以看到,master和slave都会有一个HREADY信号输入,slave产生HREADYOUT信号经过MUX后形成HREADY信号,如果刚开始HREADYOUT信号均为低,系统就会处在等待状态。

要求:HREADYOUT信号在复位后必须为高。

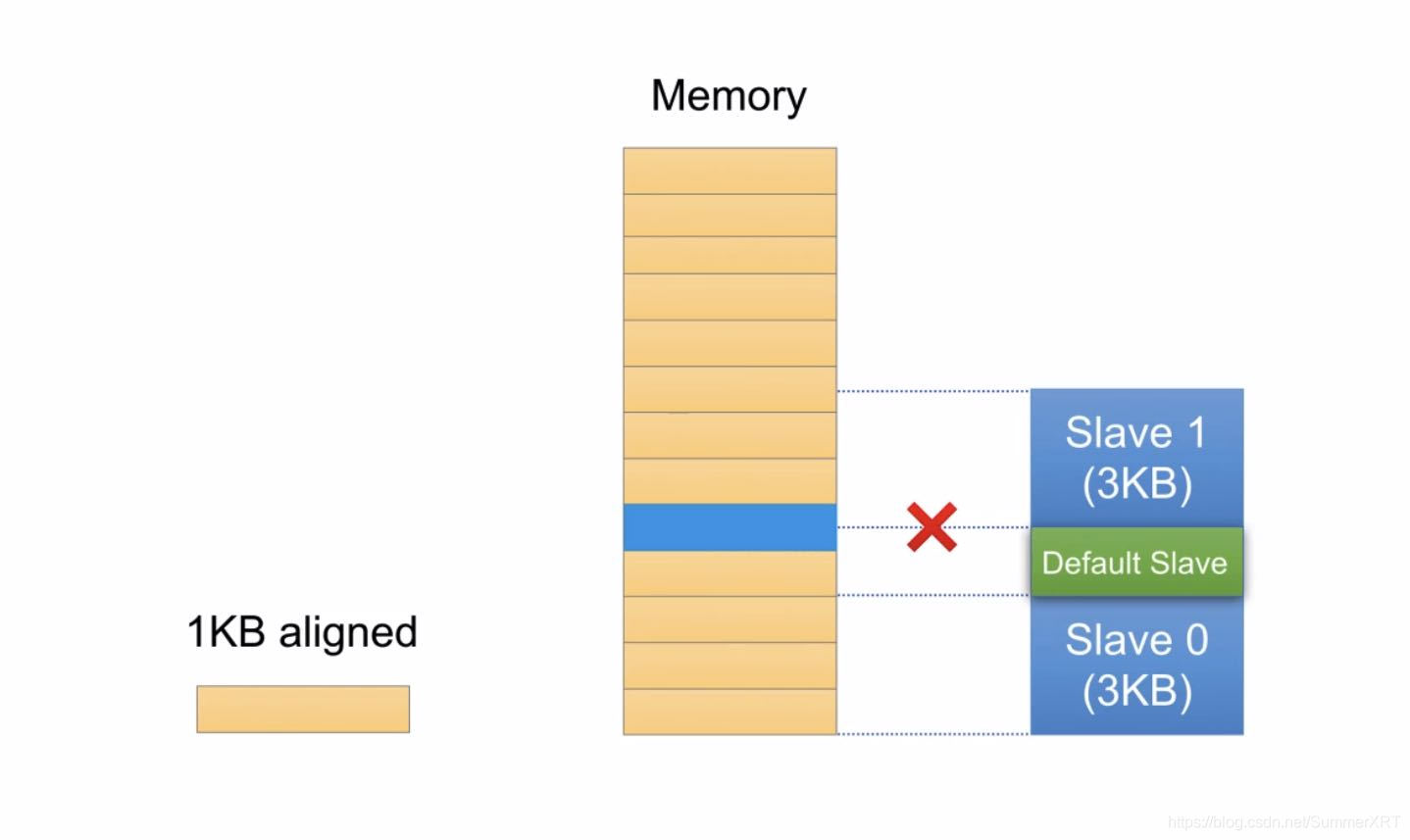

2.Memory Map的边界地址对齐

当AHB总线上的master对slave进行读写时,发出的地址经过AHB总线的译码器(通过内存映射表) 产生该地址所对应slave的选择信号,选中对应的slave;这样就可以对slave进行读写操作了。而 Memory Map是由很多1 KB 的空间(210)作为单元构成的,AHB在译码时只会译码1KB以上的地址空间(换句话说就是分配给单个slave的最小地址空间为1KB),假如slave的地址对应的是3KB,此时slave的地址映射有可能不是边界对齐的。

如下图所示:

slave 0 的地址是1KB对齐的,而slave1的地址则不是1KB对齐的,这就会导致当你访问这个“蓝色”的地址空间时,这时译码产生的这个hsel信号就会同时选中slave1 和default slave。

注:这里的default slave是指的没有分配地址的slave,因为AHB在做地址映射时,并不是所有地址值都会对应一个slave,没有使用的地址值可以使其对应一个default slave。

default slave 既可以在AHB bus做地址映射时指定,也可以在MUX中选择slave的时候指定,目的是为了防止CPU在发送访问指令后,无法正常访问。

3.Memory Attribute

设计slave时需要考虑下面两个信号。

- HPROT信号:

- 主要就是要去定义slave是可以在特权模式进行访问,还是user模式下可以进行访问,或者两种模式都可以访问。一般情况user模式下可以访问,特权模式下也可以访问;特殊的情况是特权模式可以访问,而user模式不能访问。

- Device memory要区分到底是early response还是 not early response,所谓early response就是把写的数据先放在一个write buffer里面,然后马上就可以返回一个response,这时这个写传输就可以结束了。如果是not early response的话,发送的写传输一定要生效,生效后然后才返回一个response,这个transfer才算结束。

- HNONSEC信号 :为了适配ARM的trustzone机制,有两种 secure 和 non-secure地址空间,包含static secure 和 dynamic secure机制。所谓static secure 是指non_secure和secure的地址空间分配在设计的时候就固定死的,而dynamic secure是指non_secure和secure的地址空间分配是可以通过寄存器进行配置的。

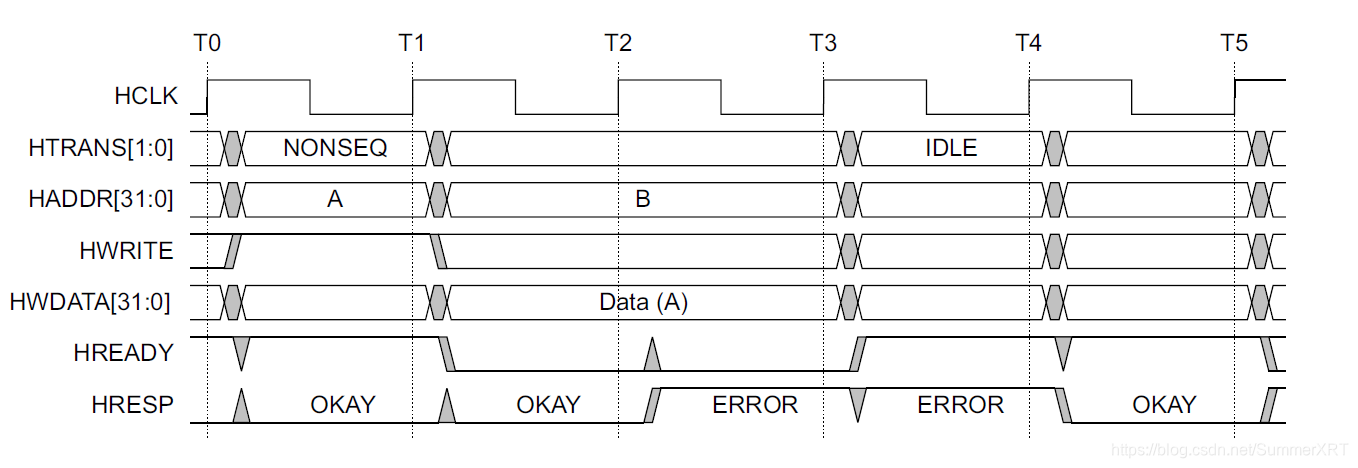

4. ERROR response

error response拉高的两个周期一定是要发生在HREADY信号上升沿附近。换句话来说,如果要有error response,那就一定要满足HREADY为低的一个周期和为高的一个周期。

5.跨时钟域的处理

AHB2APB bridge ,典型的SOC中一般AHB子系统的时钟频率在200MHZ,而APB一般在几十KB~几十兆。所以AHB2APB bridge中由高时钟频率向低时钟频率的跨时钟传输需要做处理。

- 异步FIFO

- 对于单bit可以通过打两拍或打三拍的方式

- 握手协议

6.采用寄存器寄存一拍

SPEC中规定可以将输出数据和输入数据寄存一拍,以此实现高频率传输。尽管增加一拍寄存,使得传输上延迟了一拍。如果设计中的组合逻辑延迟很大,会导致系统频率不能太高,否则会造成时序不满足的情况。当采用寄存器一拍,就会切断过长的组合逻辑的时序路径,可以采用更高的系统时钟频率。

7.Verilog设计代码

文章过长,不易阅读,所以把代码拆分在:AHB2APB同步桥的设计代码 一文中。