仿真错误描述:

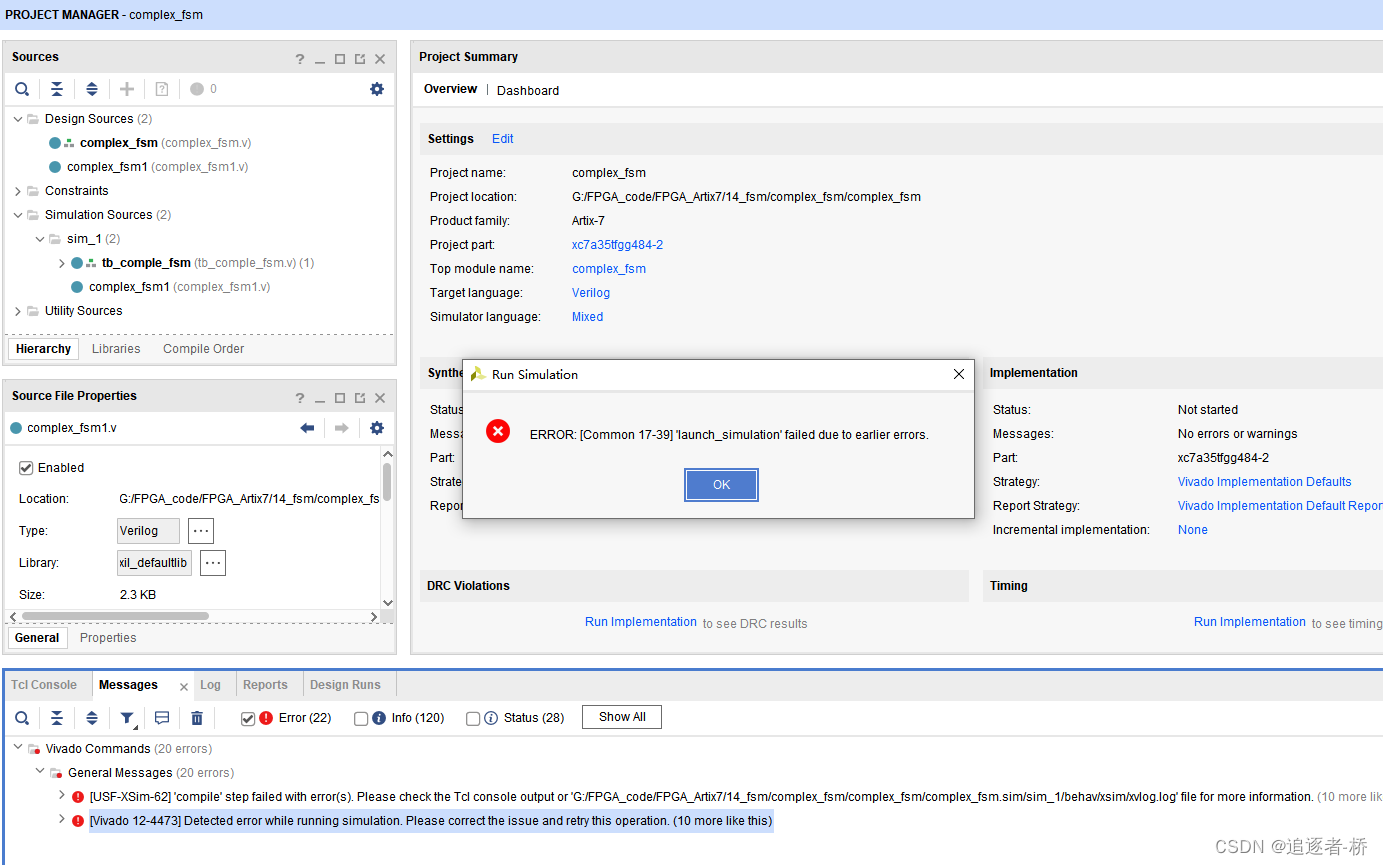

作为新手在学习FPGA时的问题,使用Verilog语言在Vivado中编程,在进行仿真时出现错误提示如下:

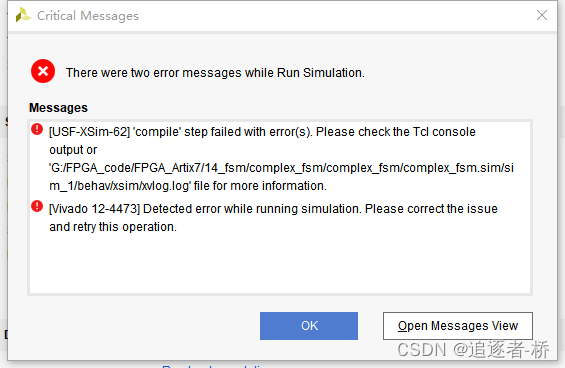

- [USF-XSim-62] 'compile' step failed with error(s). Please check the Tcl console output or 'G:/FPGA_code/FPGA_Artix7/14_fsm/complex_fsm/complex_fsm/complex_fsm.sim/sim_1/behav/xsim/xvlog.log' file for more information.

- [Vivado 12-4473] Detected error while running simulation. Please correct the issue and retry this operation.

当你会发现你的代码并无语法错误,也无法通过界面进行错误定位:

错误原因:

错误原因:

大部分是由于在你敲代码时有些变量敲的有问题,如本人出现的问题:

module complex_fsm(...);

...

reg [4:0] state;

...

...

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

po_cola <= 1'b0;

else if((stat == ONE_H && pi_money == 2'b10)

||(stat == TWO && pi_money == 2'b01)

||(stat == TWO && pi_money == 2'b10))

po_cola <= 1'b1;

else

po_cola <= 1'b0;

...

endmodule

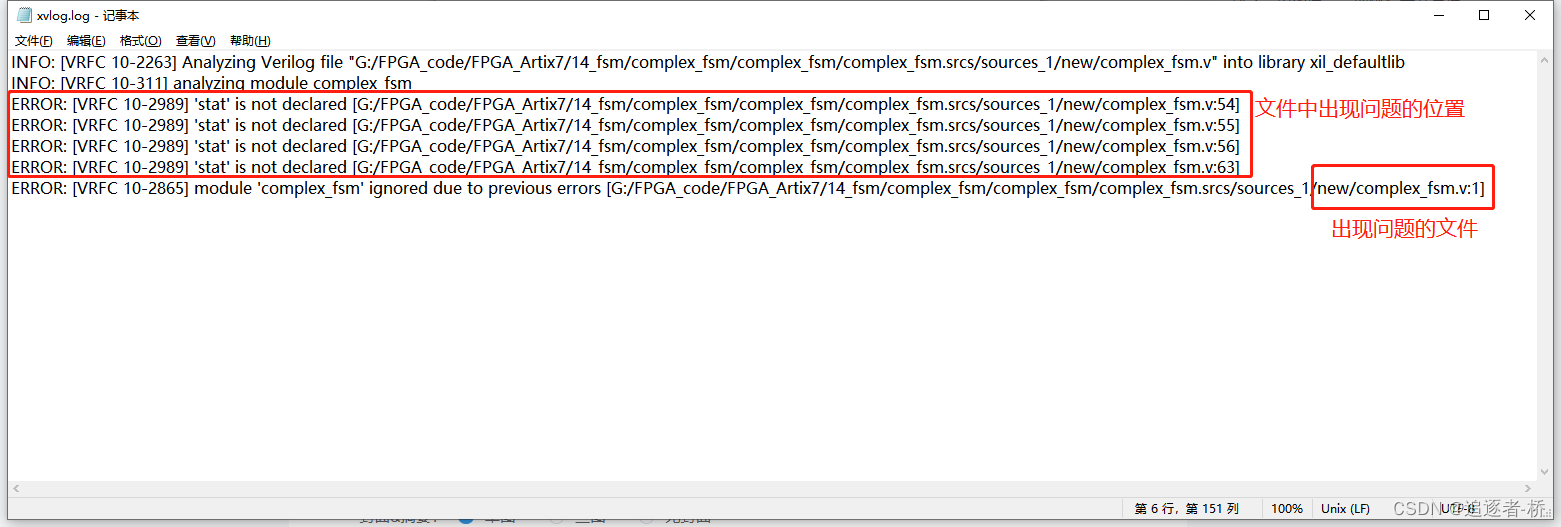

上段代码寄存器变量声明的时候为state,但是使用时少敲了一个"e",变为stat,这时不会提示语法错误,但是在仿真时会出现:

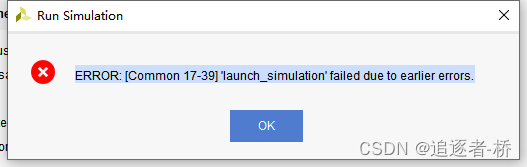

ERROR: [Common 17-39] 'launch_simulation' failed due to earlier errors.

解决方法:

针对少字母的问题,如何查找出错的位置,首先不能使用语法错误定位。这里Vivado会在仿真时,生成一个问题描述文件:xvlog.log,其位置在Vivado的错误提示中会有显示:

[USF-XSim-62] 'compile' step failed with error(s). Please check the Tcl console output or 'G:/FPGA_code/FPGA_Artix7/14_fsm/complex_fsm/complex_fsm/complex_fsm.sim/sim_1/behav/xsim/xvlog.log' file for more information.

拿本人的错误代码为例进行说明:

通过该文件可以定位到错误的位置,可以查看相应的代码。改过相应的代码即可解决该问题。

如果该问题通过本博客解决,请大家三连一下,本人将继续在FPGA和硬件方向继续发优秀的博客

谢谢大家的支持!