一、实验要求

(1) 时钟功能: 采用数码管显示累计时间,以24小时为周期。

(2) 校时功能: 能快速校准“ 时”、“分”、“ 秒”的功能。

(3) 整时报时功能: 具体要求整点前鸣叫5 次低音( 500 Hz ) , 整点时再鸣叫一次高音(1 000 Hz左右) , 共鸣叫6 响, 两次鸣叫间隔0 .5 s。

(4) 计时准确: 每天计时误差不超过10 s。

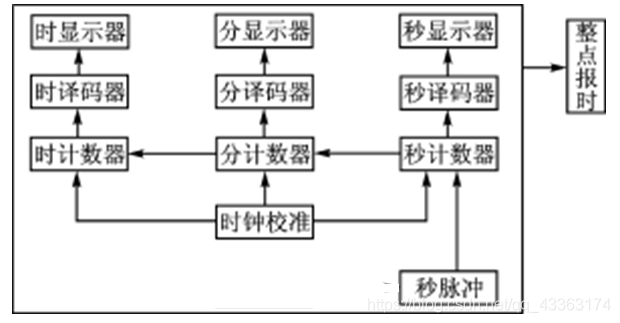

二、设计方案

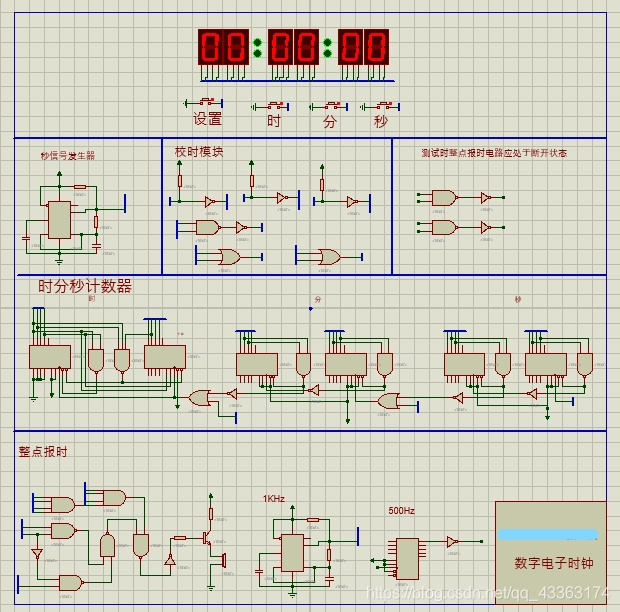

采用74LS161作为计时器,分和秒利用74LS61级联构成60进制计数器,时利用74LS161构成24进制计数器;秒信号发生器由555振荡器、电容和电阻构成;校时模块用与非门与组合逻辑电路实现。整点报时电路则可利用74LS192、蜂鸣器以及逻辑门构成。

三、功能模块

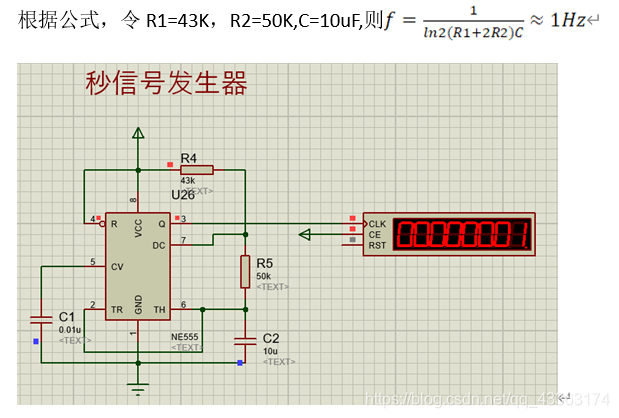

- 秒信号发生器

本模块由555振荡器、电容、电阻组成

具体电路图如下:

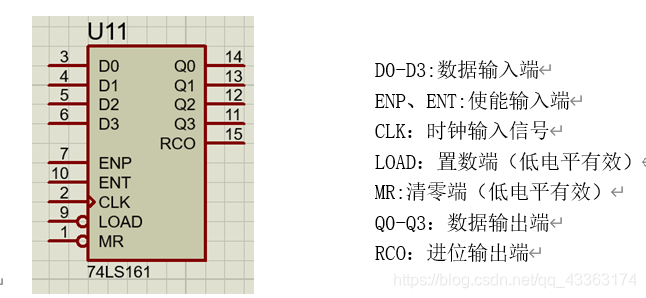

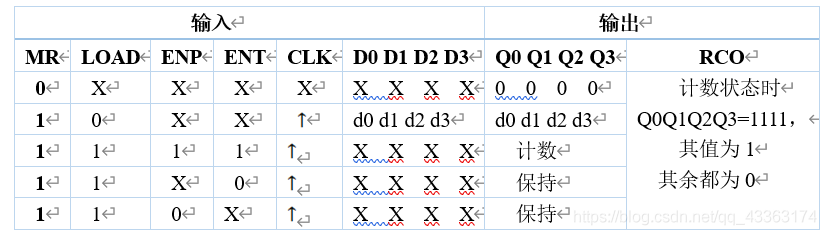

- 时分秒计时电路

本模块由四位二进制加法计数器74LS161和与非门、非门构成

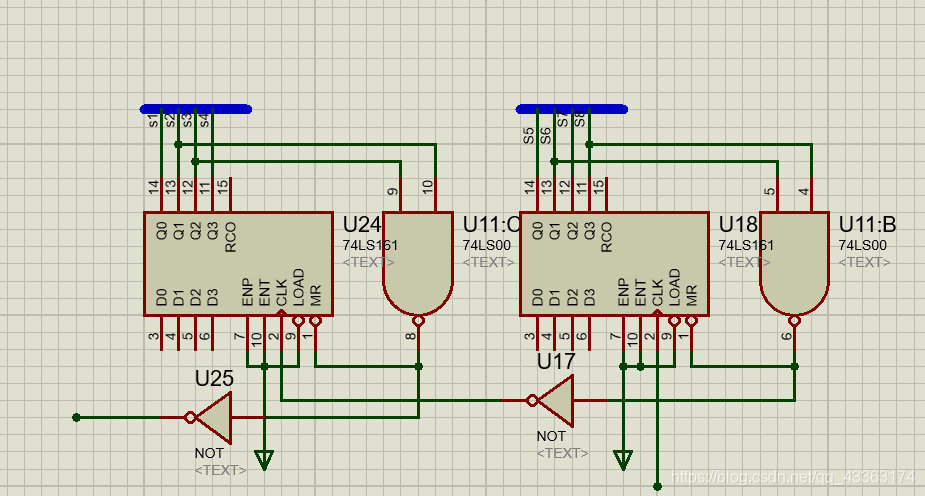

故六十进制计数器如下:

如上图,将低位芯片的MR信号通过非门连接到高位芯片的clk端,即对秒信号进行了一个十分频,高位芯片每十秒计数一次,计到Q3Q2Q1Q0=0101,再来一个脉冲MR=0立即清零。整体实现了60进制计数器。

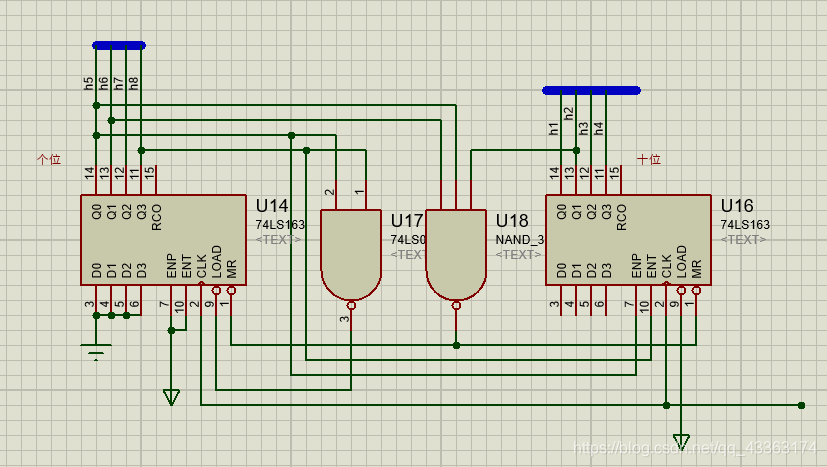

二十四进制计数器如下:

如上图,将高位的ENP、ENT分别接到低位Q0,Q3,仅当输出1001,并且再来一个脉冲的情况下,高位才会计数,满足了级联芯片的进位条件。

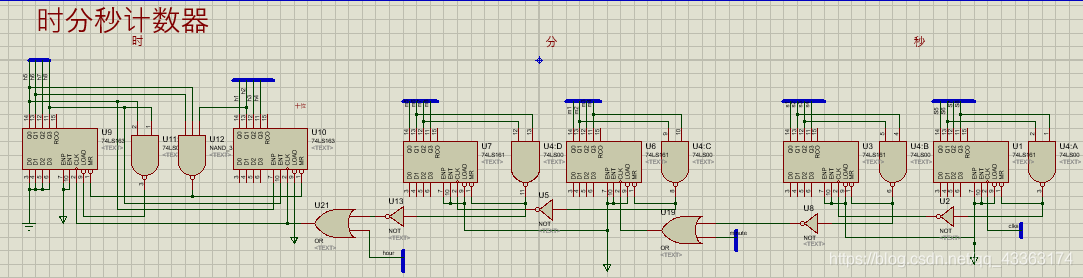

时分秒计数器级联如下:

-

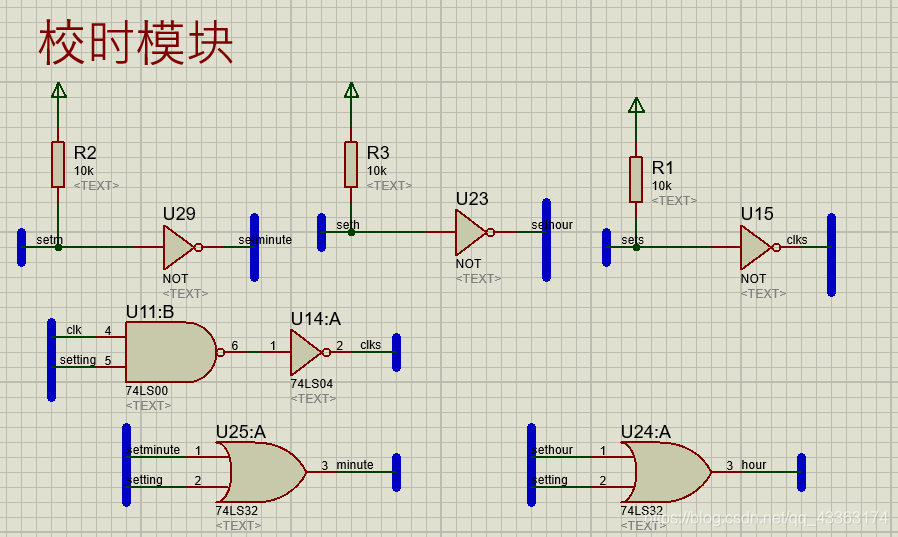

校时模块

本模块主要由各种门级电路和按键组成。

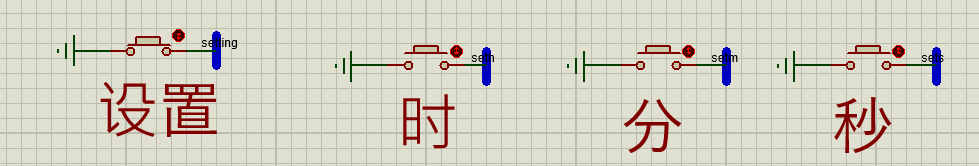

首先得有校时总按键,然后要有三个分按键,分别调节时分秒。电路如下:

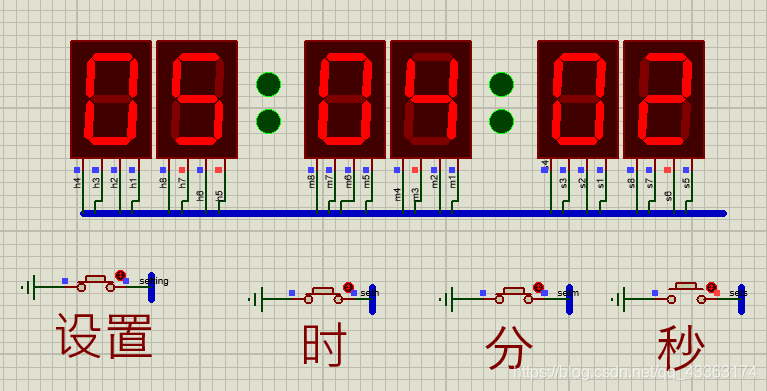

按下设置按键后电路要停止计数,再按下分按键后相应的时、分或秒应该产生一个上升沿脉冲,使相应的位数加一。具体电路如下:

以设置分为例,未按下设置按键时,setting高电平,通过或门后minute始终为高电平,不会产生上升沿,只有当按下setting后,再按下setm才会产生上升沿,分计数器才会加一。同理,设置时也是如此。至于设置秒,按下setting后clks始终为0,计数停止;再按设置秒按键,clks变化,显然秒会加一。 -

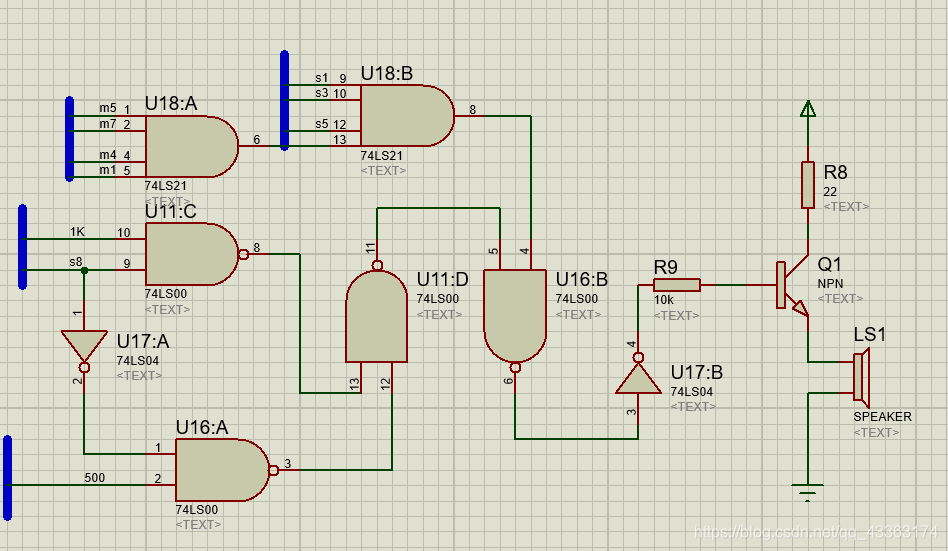

整点报时模块

由要求知,要在鸣叫5 次低音( 500 Hz ) , 整点时再鸣叫一次高音(1 000 Hz左右) , 共鸣叫6 响, 两次鸣叫间隔0 .5 s。故可设计电路如下:

开始鸣叫时,显然m5=m7=m4=m1=1,s1=s3=s5=1时,并且s8=0时SPEAKER端的信号随500Hz脉冲的变化而变化,进行低鸣叫;59:59时,SPEAKER端的信号随1KHz脉冲的变化而变化,发出高音鸣叫。

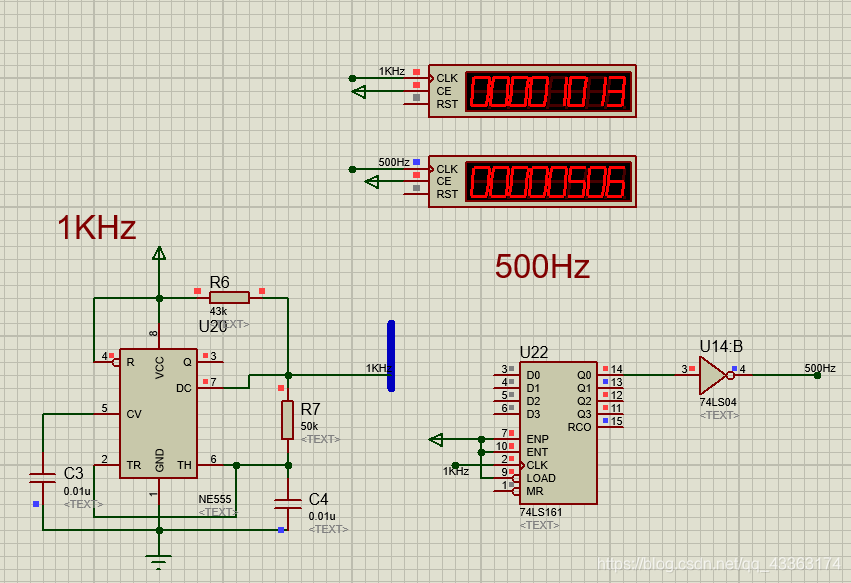

1KHz脉冲信号和500Hz脉冲信号如下:

其中1KHz信号由555振荡器产生,根据秒信号发生器计算公式,知只需将C变成0.01uF即可;500Hz信号可由74LS161构成二分频器,如上图,将Q0通过一个非门即可得到500Hz脉冲信号。

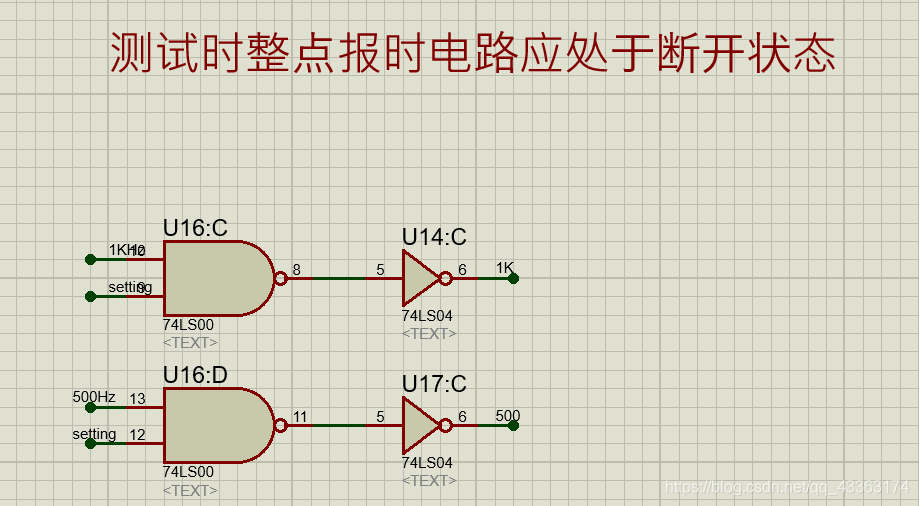

同时考虑到校时时整点报时模块不可以工作,所以将1KHz脉冲、500Hz脉冲输入做如下变换:

按下设置键后,setting=0,1K和500均为0,整点报时模块无脉冲输入

四、总体电路图

五、实验结果

校时:

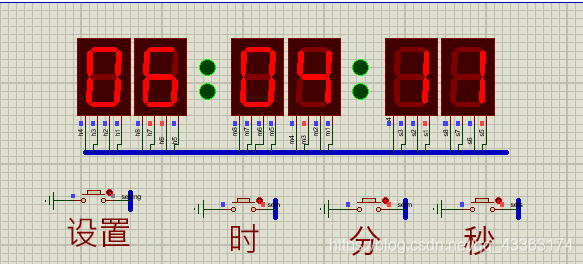

正常计时:

附、下载链接

数字电子时钟