计算机硬件系统设计(华科)——运算器设计(Logisim 实现)

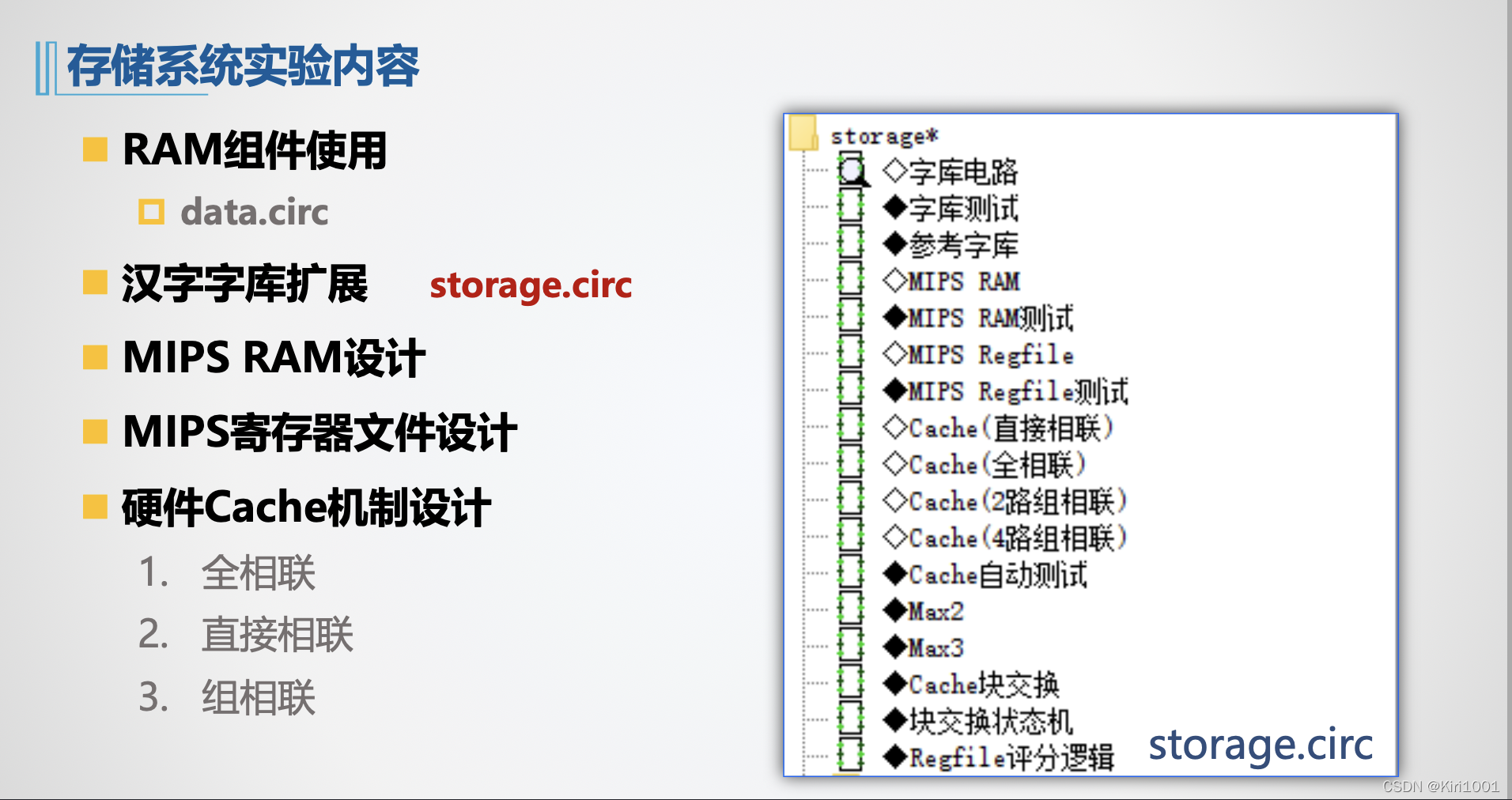

- 前言

- 汉字字库扩展

- MIPS RAM 设计

- 片选信号

- 写入与读出控制

- MIPS Regfile

- Cache映射机制与电路实现

- 直接相联映射

- 全相联映射

- 2路组相联

- 4路组相联

- 总结

前言

本章将继续介绍《计算机硬件系统设计》的关于存储器设计的内容。内容不尽完善,如有疑问欢迎评论留言,共同探讨学习。

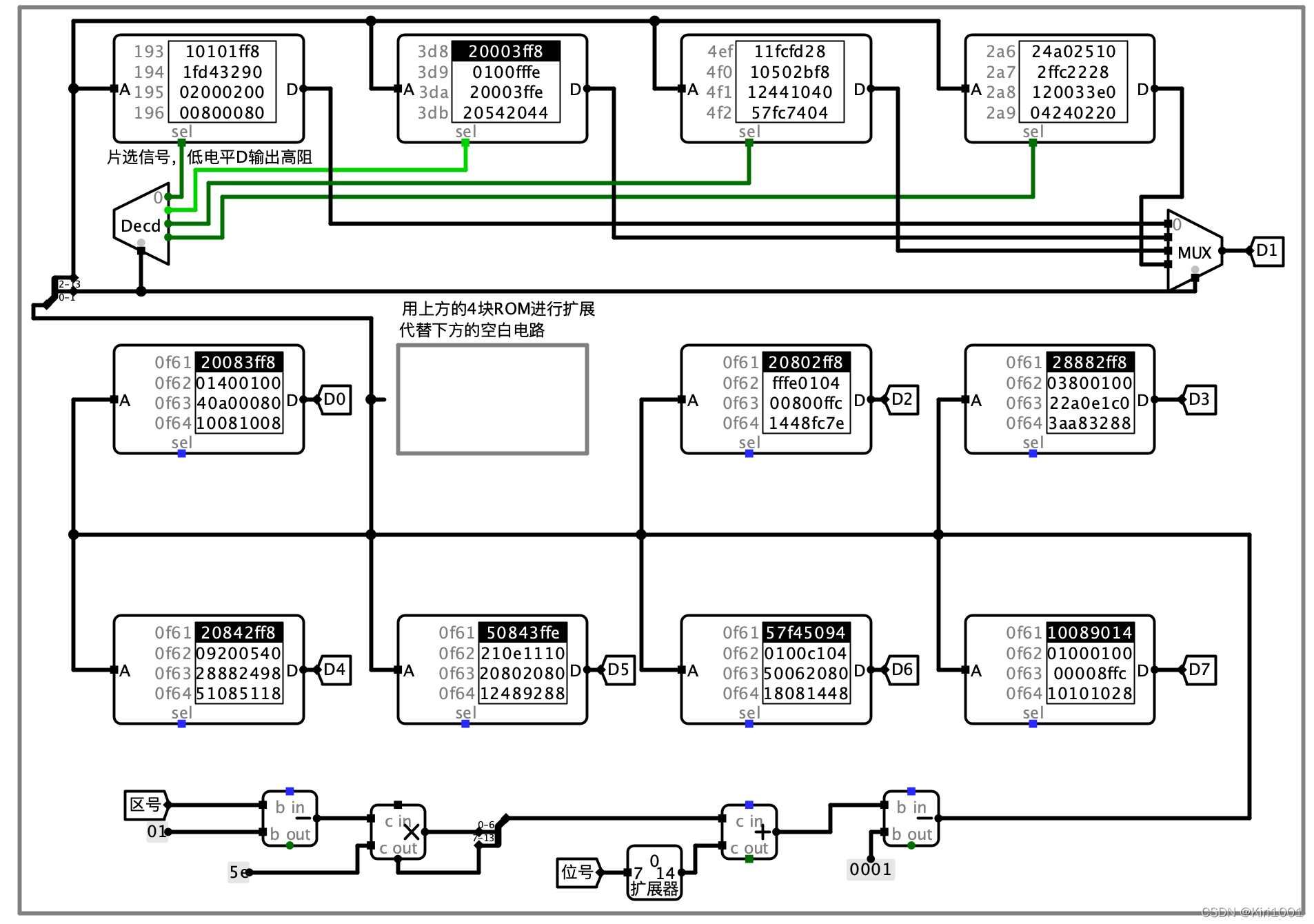

汉字字库扩展

理解字扩展、位扩展基本原理。汉字显形本质是通过LED点阵显示字形,例如使用16*16的LED点阵,显示一个汉字则需要256位的二进制信息,通常没有如此庞大的字长存储器,所以需要使用位扩展以存储信息。

如 Logisim 中提供位长32的存储器,故需要 256 / 32 = 8 片存储器。

实验设计以GB2312编码为标准,GB2312 设计分区94个,每个区94的汉字,故使用

逻辑地址 = (区号 - 1)* 94 + (位号 - 1) 【区号、位号从“1”开始编号】

编码详情见:GB2312 标准

通过课程文件夹中给定的编码文件,进行合理划分并写入ROM,在数据寄存器的配合下以显示汉字。

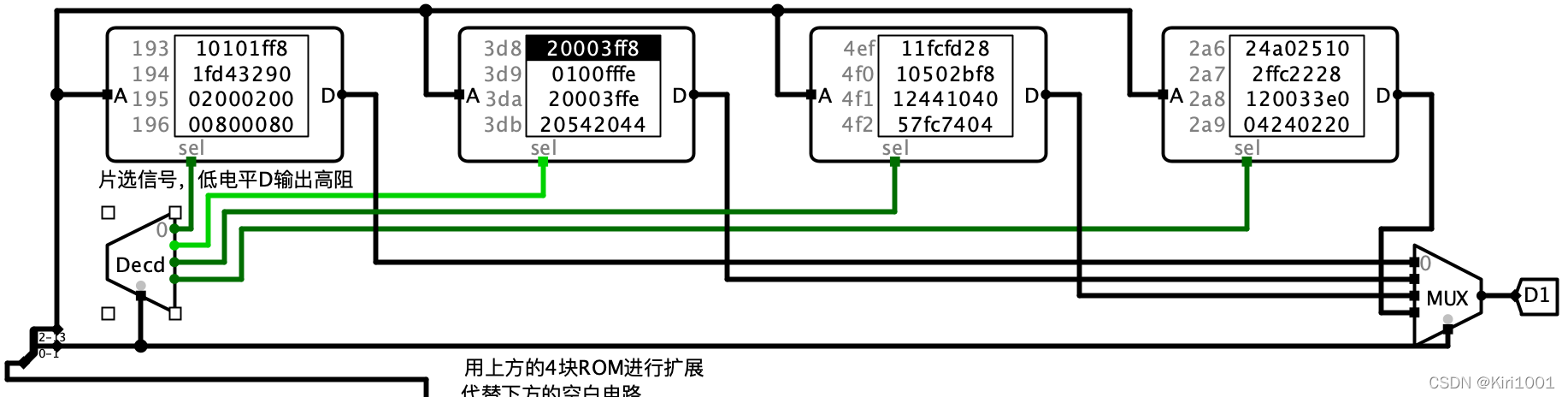

进行字扩展时,高位做为地址信号,低位做为片选信号,使用译码器和多路选择器已实现数据的选择。

ROM中数据需要通过课件中字库数据文件进行二次划分,将对应数据写入对应的存储器中。

MIPS RAM 设计

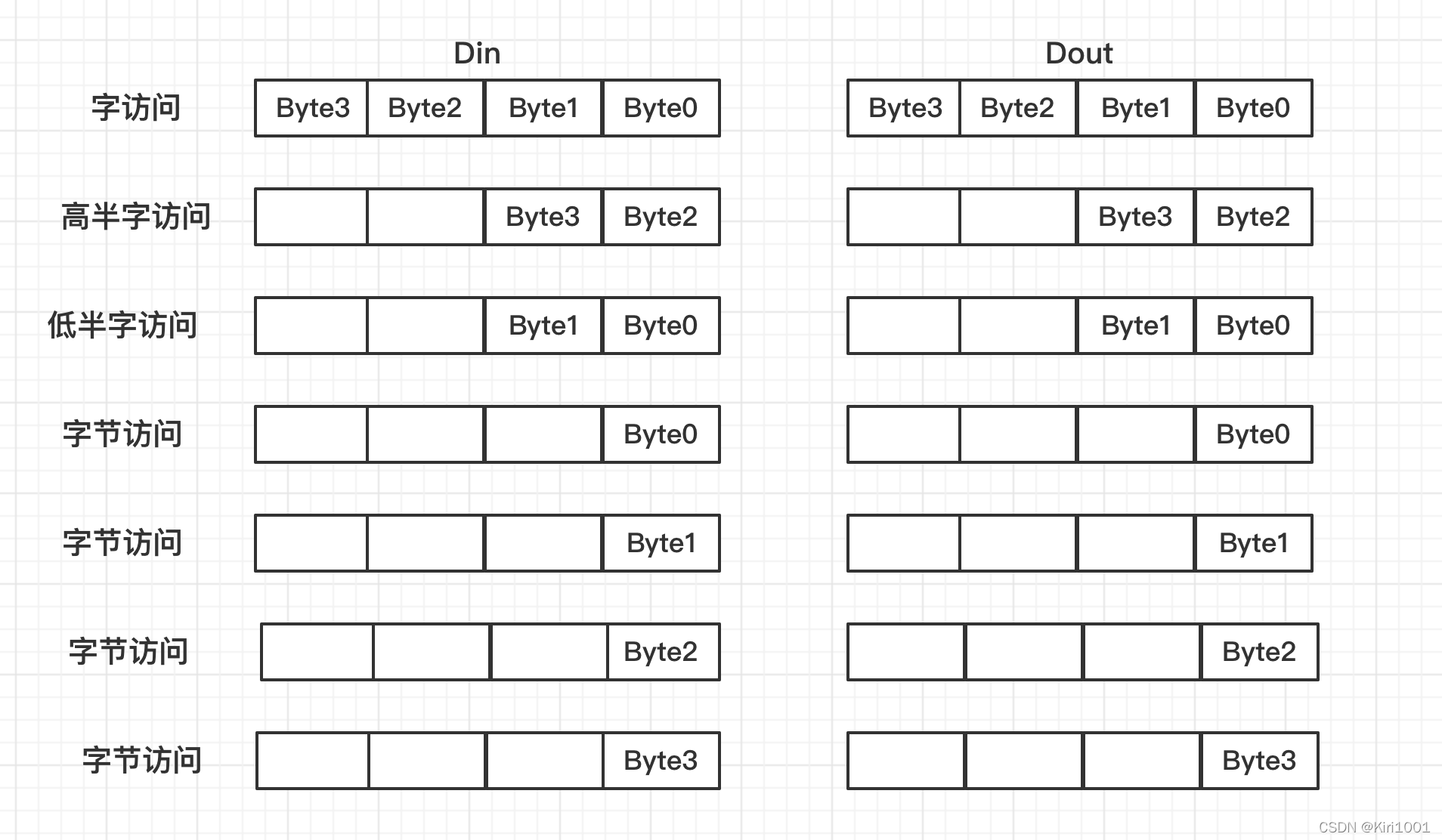

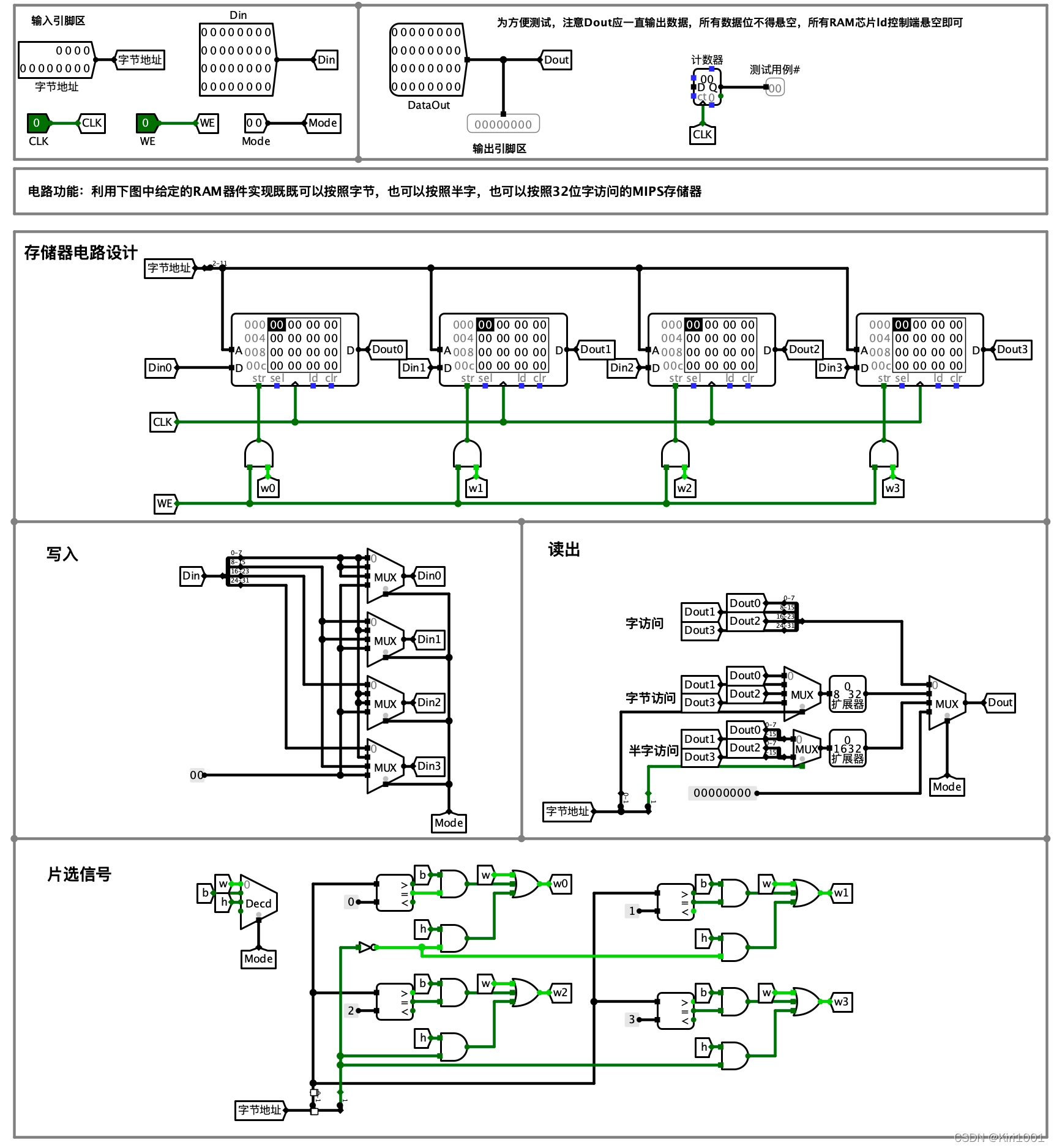

构建支持字节访问,半字访问,字访问的存储系统,实现可变数据位宽,与实际计算机的存储系统相似。

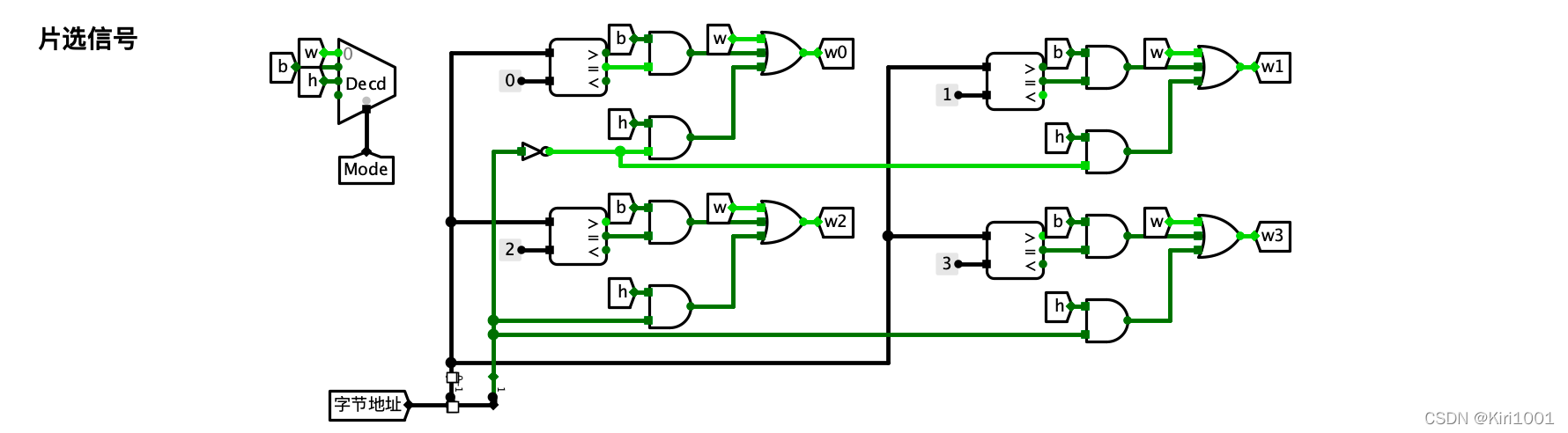

片选信号

访问模式信号通过译码器确定访问方式。字节访问时,根据地址低两位确定存储器选片;半字访问时,根据第二位选择是高位数据还是低位数据;字访问设计最为简单,需要访问所有RAM片。

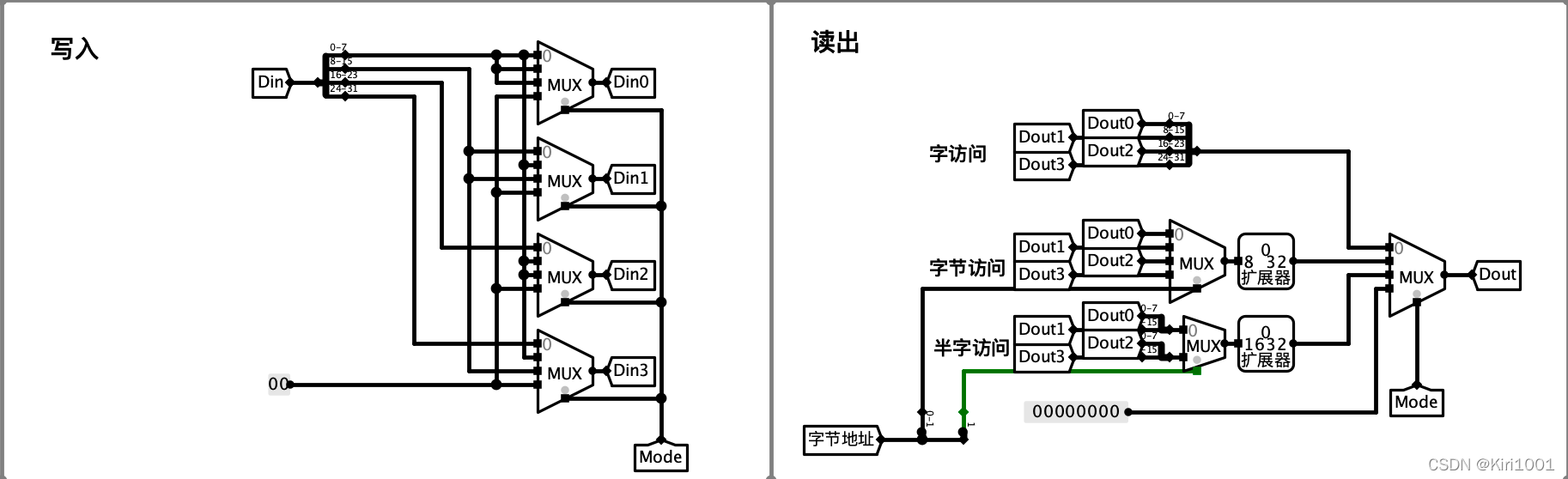

写入与读出控制

使用多个多路选择器,控制选择器输出具体数据。写入控制,读出控制的逻辑比较简单。具体如图。

设计电路时主要注意数据位宽和数据对应的逻辑位置即可。

最后实现存储器电路设计。

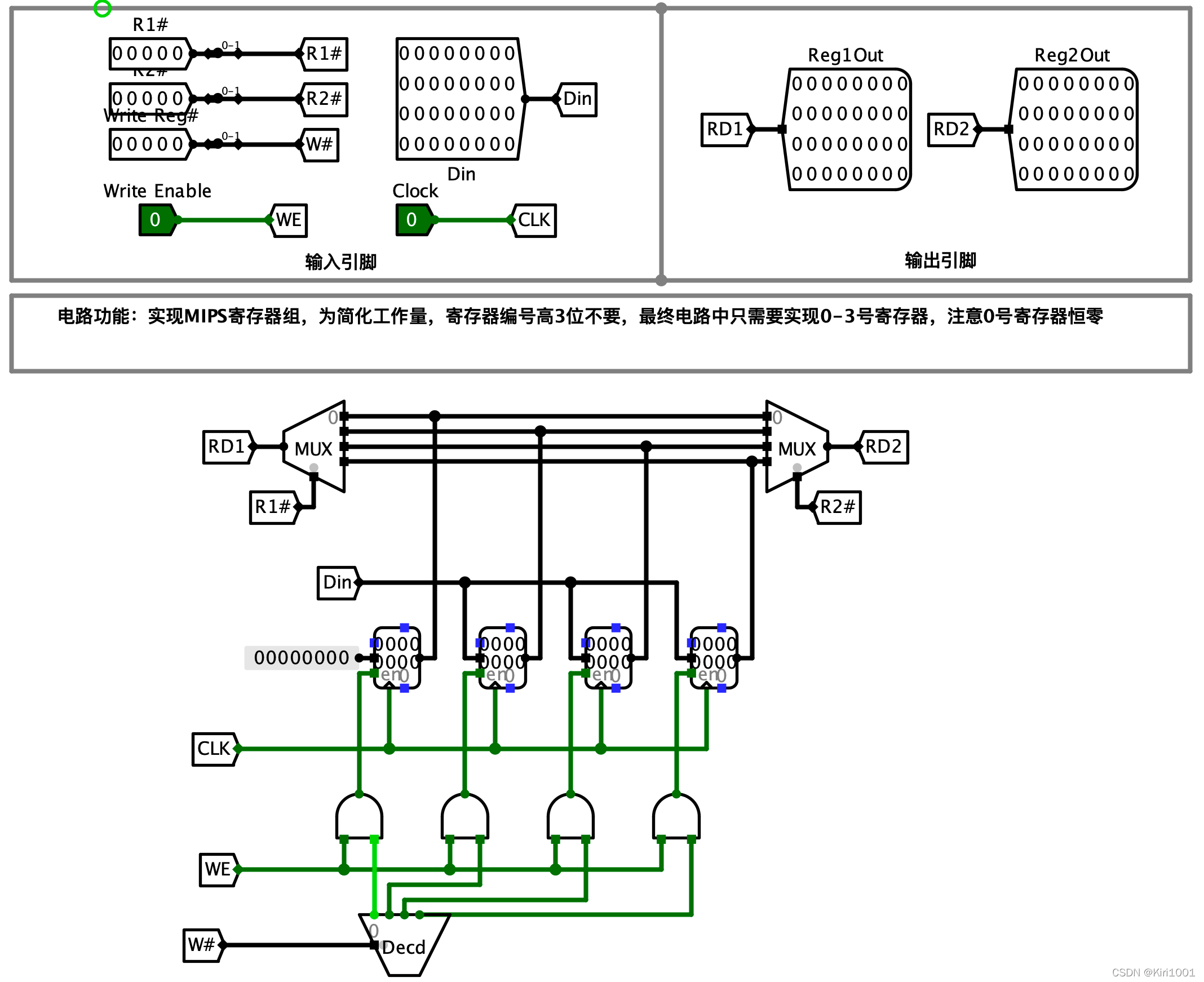

MIPS Regfile

该组件的设计需要求是源于MIPS指令集的设计,具体可以参考MIPS CPU相关要求。设计逻辑也比较简单,如图。不再赘述。

Cache映射机制与电路实现

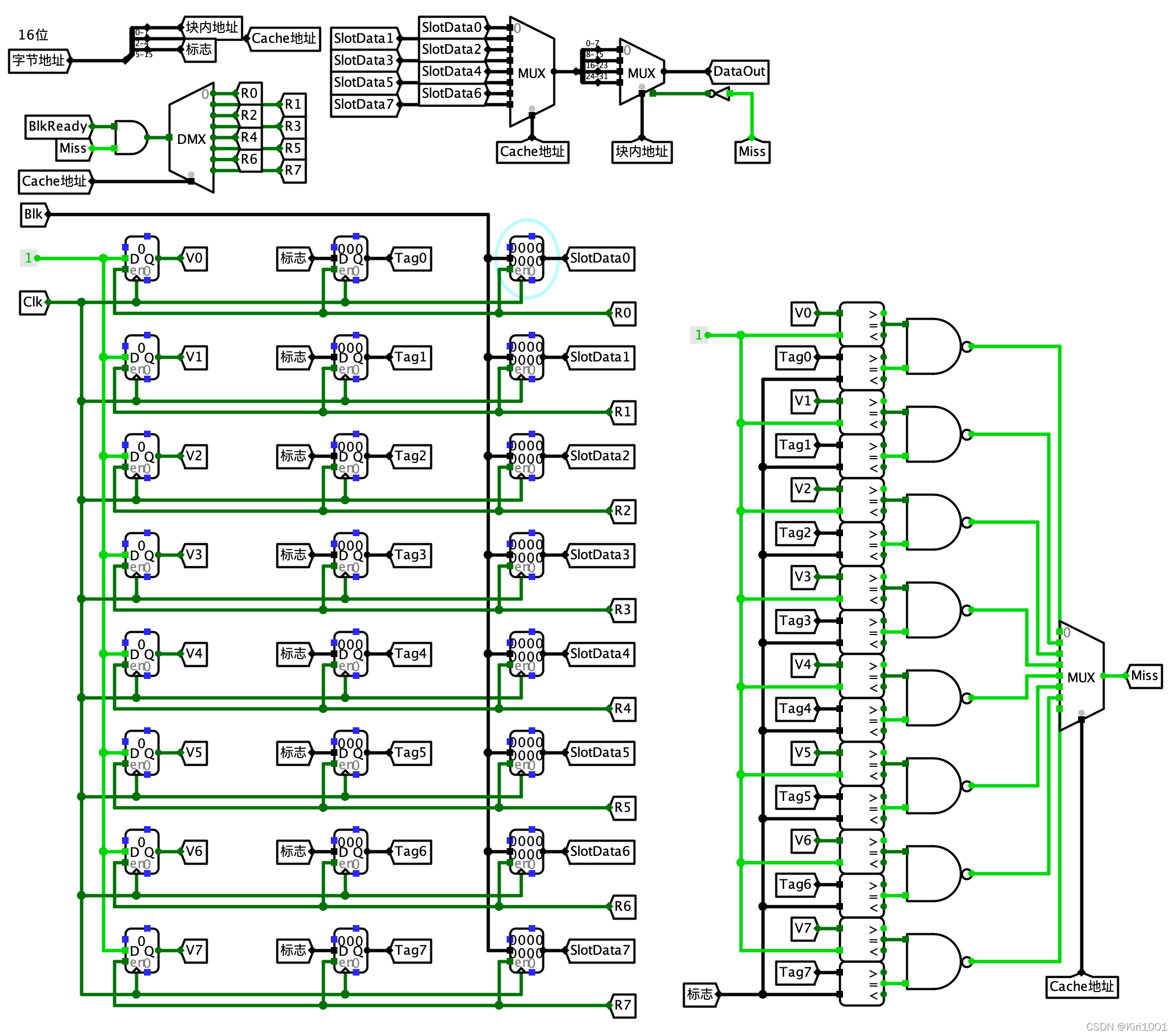

直接相联映射

主存中某块会被放置于Cache中固定位置。

设Cache块号为 i,共n块,主存块号为 j,则 i = j mod n

由此可以将主存地址分为三部分:区地址 + 行地址 + 字地址

行地址可以确定数据存在Cache中具体哪一行,字地址按照读取方式确定,区地址明确数据位于主存哪一区。Cache行中除了设计数据寄存器,还需增加区地址寄存器,有效位标记寄存器等其他(按需)。具体设计如图。

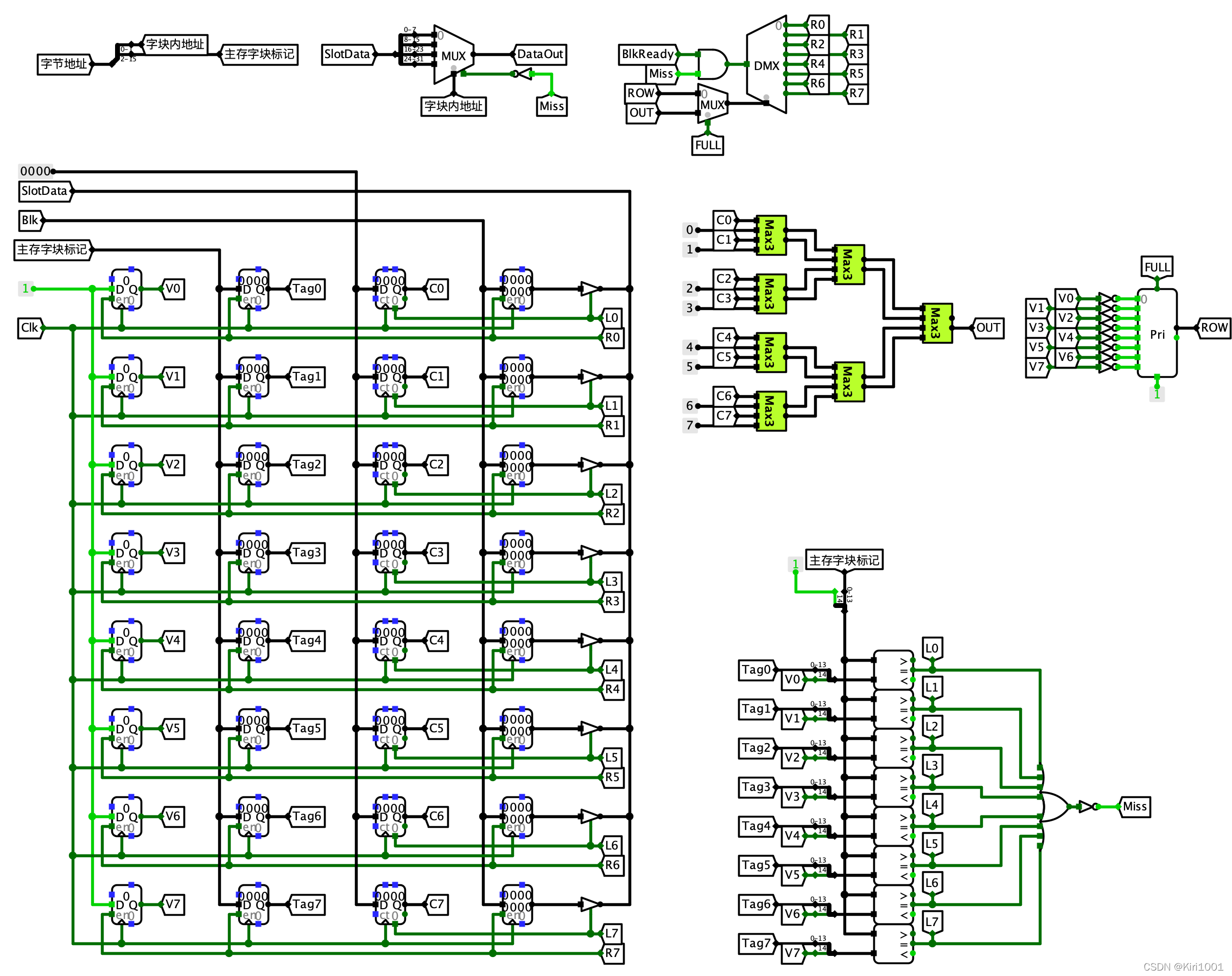

全相联映射

主存数据块可以放置于Cache中任意一块,因此Cache在记录数据块地址时,需要记录其在主存的地址。Cache在命中比较时,使用Cache中所以行中的主存标记并发比较,以判断命中与否。

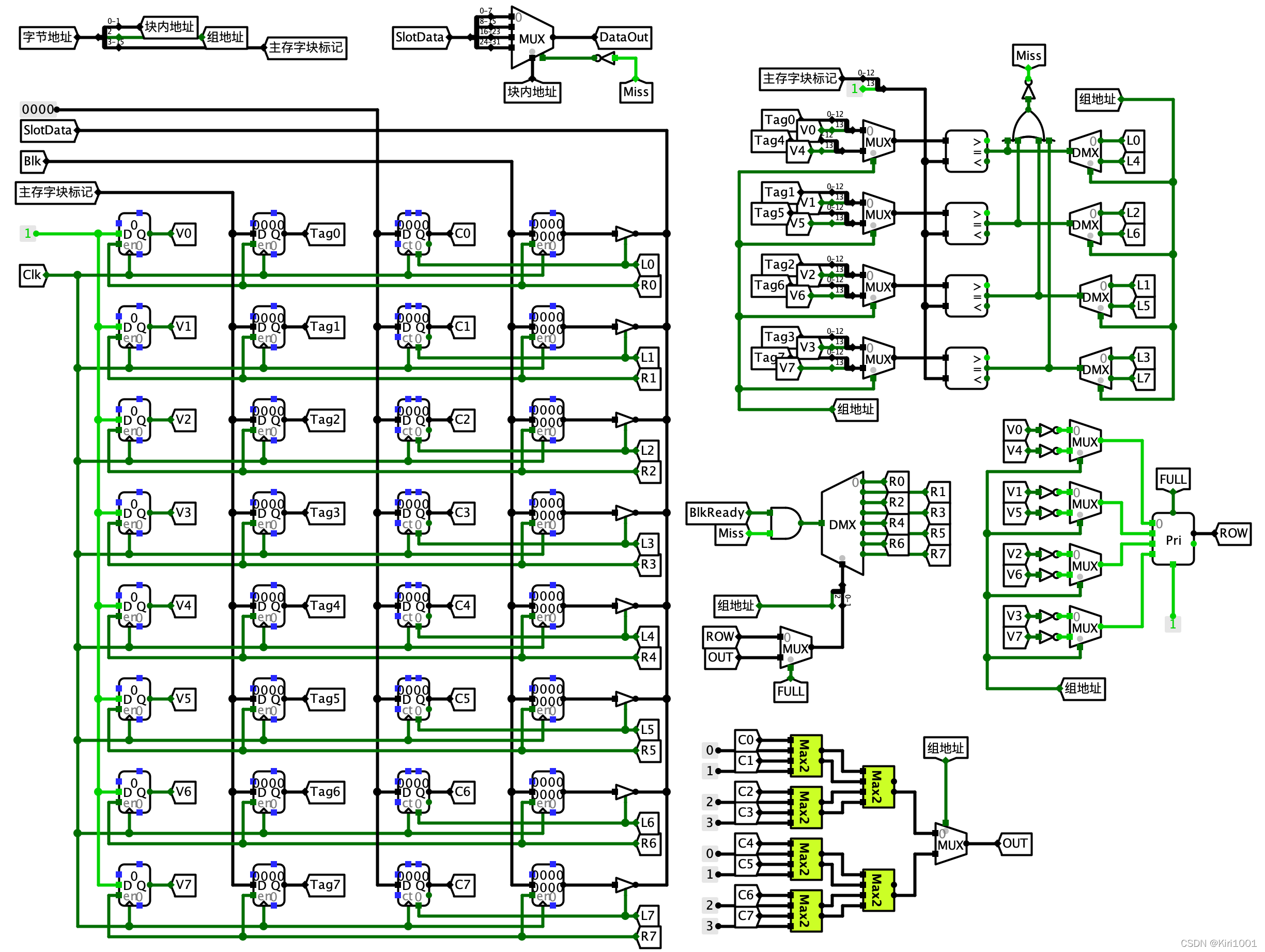

2路组相联

4路组相联

总结

以上为存储器设计实验,实验难点在于Cache的设计与映射机制,多路组相联中没有再详细介绍,具体的映射逻辑可以参考MOOC中的讲解。

实验设计中有任何问题可以在评论区留言,希望可以和各位进行探讨,共同进步学习。